在讨论如何设计产品避免遭受ESD损坏之前,先要了解ESD破坏电子产品的原因,方便后续讨论与技术的了解。 ESD能量是经由传导性能量转移方式引入产品的电子组件内,主要破坏力是瞬间峰值电流,电压是引导放电作用的诱发位能。ESD开始时是经由直接(电流)或间接辐射方式以快速的瞬时突波冲击到电路组件上,这当中有电流热效应也有电磁场的干扰效应。

故ESD 对造成电子组件失效情况可概分三种情形, (1) 硬件失效(Hard failure),(2) 潜在性失效(Latent failure)和 (3) 场强感应失效 (Field induction failure) 。

1. 硬件失效问题: ESD电弧电压(Spark voltage)窜入半导体内部使绝缘部位损坏. 如在P-N接合点短路或开路,内部绝缘的氧化层贯穿(punch-through)-金属氧化处理部位产生熔蚀(melting)等, 这都是属于永久性失效.

2. 潜在性失效问题:当ESD发生时系统虽暂时受到影响,仍然可继续动作, 但功能会随时间逐渐变差, 隔数日或数周后系统出现异常, 最后成为硬件失效. 这是因为半导体组件已经受到部分不可回复的损伤, 随着使用时间日增,异常功能自会逐渐显现. 这种失效是最难捉模,无法以失效模式分析确认. 若用户若遇这类产品, 应该要能意识到该产品的质量状况,尚不成熟。

3. 感应场强失效问题:当 ESD的高压放电火花跟电流会对产生电场辐射效应, 这种宽带的辐射,经常使临近的电路受干扰而失常,如Latch-Up,或暂时性程序错乱,及数据流失等,严重时更会损伤硬件成为永久行硬件失效。

ESD的防护设计由PCB 阶段开始做起

谈到系统产品的静电防制设计, 必须从印刷电路板(PCB)开始做ESD的保护. 在印刷电路板上也有三种容易造成ESD失误状态如下:

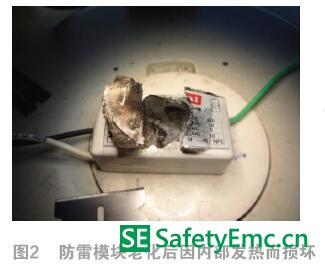

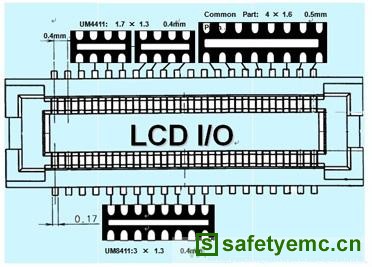

1. ESD电流直接流经受害电路组件的接脚造成永久性损坏: 此类模式系由外部组件(如键盘, 或I/O界面的连接器)直接联机带入ESD突波电流. 要预防这种直接伤害, 即使用一颗串联电阻或并联电容在这些电路上就可以限制流经IC的ESD电流,如图1,图2。

2. ESD电流流经地回路造成重置或损坏: 大部份的设计者都假设其电路接地为低阻抗, 经ESD脉充电流通过, IC接地的阻抗极容易产生地电位跳动(Ground Bounce), 这种地弹跳会使IC重置或锁定, IC如被锁定时非常容易被供应的电源摧毁.

3. 电磁场间接耦合: 例如垂直板与水平板之放电, 使电路造成重置,对于高阻抗组件曾经有损坏之报告,这种失效模式与PCB环路面积,机构屏蔽好坏而定。欲防护这种ESD可以从机构屏蔽和PCB设计布线着手。

在PCB上对ESD保护常用之设计技术

• PCB走线排列时加放电间隙,这是用一组锐角三角形铜箔尖端相对,间隔约6-10 mil,其中一端接地。参阅图3所示。

• PCB走线须考虑减少对电磁场耦合的敏感度,多应用反耦合电容,可减小回路面积。反耦合电容宜选用耐高压的陶磁电容,这些电容必须放置在靠近I/O连接器处。 如图4所示之例子将耐高压的陶磁电容放在PCB连接器附近的VCC 和Ground,这不仅缩小了环路面积,也收到反耦合( decoupling)的作用. 另在电源及地之间加上高谐振频率的旁路电容,可降低对感应场强及电磁场间接耦合的反应,唯电容的等效串联电感 (ESL) 及等效串联电阻要越低越好。

• 在PCB 布局时可以使用低通滤波的方式疏导ESD能量,低通滤波器是由电容与电感组合构成,它可以阻止高频的ESD 能量进入系统。其中电感对突波会呈现高阻抗,因而衰减了窜入系统的能量, 电容是装置在电感的输入端,会将窜入的ESD高频频谱能量旁路到接地端。 如图5。使用环氧铁质( Ferrite)电感对ESD电流有极佳之衰减能力。

• 在PCB上可用箝制电路抑制瞬间高压如图6, 图7. 如使用电压箝制二极管作抑制,在规格上必须选择能承受数kV之耐压且dv/dt脉冲响映快速, 并能在瞬间消耗大电流的二极管组件.

• 在PCB部局时可将对ESD敏感组件以壕沟方式与其他区域隔离, 以防止ESD事件的转移或耦合到其它功能的部位.

• 对间接放电的电磁场耦合及电弧效应场强辐射抵抗力而言,采用多层板比单层板可增加10倍以上的免疫力.

系统之产品ESD防护

在系统阶段的静电防制措施,最主要是从接口的连接阜作好接地,另外机壳若为金属材质, 如要做表面处理前,机壳或机构在衔接位置务必保持导电性, 如此才可以使机壳发挥屏蔽功能。若ESD打在机构屏蔽良好的产品上,理论上机构内的电路是不会受影响的,这就如同以前物理学家法拉第曾经坐在金属笼试验原理相同。 但是电子产品须要有开关及按钮,因此要防止ESD能量从开关或按钮进入电路板伤及组件,可采用导电材质的垫片或垫圈(Gasket) 以阻挡ESD 电流如图8所示。

目前大多数的消费性电子产品机构外壳是使用非金属材料,例如使用塑料质外壳,是可以免测直接接触放电项目,若其绝缘与耐压特性不足,在被测试空气放电 (Air discharge)时,ESD电弧会穿透外壳或从机构隙缝窜进产品内部对PCB上的IC形成二次放电 (Second arcing) 的情况。如图9所示,要预防这种静电问题,可在靠近缝隙的位置旁加一片金属阻隔并接地,一般称之为辅助接地。

塑料外壳的电子产品对ESD脉冲电磁场强不具屏蔽功能,当遇到垂直和水平金属板的间接放电测试时特别容易受到影响,对策是要从电路板的布局减小回路面积或使用双层以上电路板,以有效降低对ESD电磁场的感应。

故定在机壳的接口连接器须有接地防护措施,其信号线可视需要状况选择用二极管或电容或突波吸做旁路保护如图18。对接口连接线 ( I/O cable) 要使用环氧磁磊挟扣(Ferrate core) 抑制ESD电流流窜到主要控制电路。但是用电容器旁路时必须留意电容器未置,如位置不对反而会把ESD电流引到主电路影响IC组件,如图10。

在系统接地方式宜采用单点对机构(机壳)接地,如图11 当高频的ESD电流经机壳至地的路径,因有接地电阻存在,对ESD电流经不同的接地点,会产生共模噪声电压(V1、V2)干扰系统功能。 因应对策是使用单点接地如图12。

故定机构或机壳的金属螺丝不宜穿透到内部,如图14所示它会形成辐射天线,当ESD对该螺丝做接触放电时,则ESD能量完全经由该螺丝对内部辐射及作尖端放电。如金属外壳有开孔未加保护处理, 则经过表面的ESD电流会透过该槽孔对内产生辐射,如图13。 保护对策如图15之右图加辅助接地隔离。

结语

对于电子产品ESD的防护应从设计着手,所谓“Designed-in at the device”,从零件的选用,PC板的设计时间,到成品系统布线整合,每个阶段都不能草率. 对于ESD让电子产品失效之三个因素:瞬时涌入的大电流的热效应,和电压漂动及静电辐射场强等都必须同时加上对策。由其在PC板布局是关系到电子产品对ESD敏感度, 这是可运用PC板布局设计技术控制, 而对MOS,Bipolar等IC组件之ESD防护能力相对较弱. 需从半导体设计源头做起。半导体设计ESD防护是最难的一环,期望在大加家的努力下,不久半导体业可以突破目前的瓶颈,推出功能稳定且可以抵抗ESD 的IC供系统产业界使用。

苏公网安备32050802011615号

苏公网安备32050802011615号