本系列文章的第一部分涵盖了抖动 (jitter) 的基本观念,包括与ADC频率相关的抖动,以及取样讯号对抖动的影响,推导出由抖动所造成的SNR基础表示式。接着,讨论了不同的类型的抖动与其来源,以及取样-频率相位噪声与抖动间的关系。总结前文,其以图表描述时序装置的功能性方块及可达成特定应用所需效能的可调整参数。

本文为第二部分,着重于设计的系统层次,一开始将检视特定的从多模块、单频道架构到单模块架构的通讯系统等问题。单模块架构藉由取样在高中频的宽带、多频道讯号,将多频道处理转移数字领域,这些架构通常使用亚奈取样 (sub-Nyquist sampling)。接下来会讨论ADC效能演进的含意并且回顾在亚奈取样下取样频率相位噪声的影响。最后阐述如何分析与此频率抖动相关的多重、无相关的噪声源对整体SNR的影响,并且举例描述针对不同的ADC分辨率要求不同的抖动。

在多媒体领域中有一项重要的趋势,也就是扩展数字化的疆域,以获取由摩尔定律 (Moore’s Law) 与其它数字领域已建立的既有优势。但由于模拟电路并未遵循摩尔定律发展,因此在尺寸与功耗方面,在模拟领域中并未像数字领域世界取得重大进展。有鉴于上述因素,通讯系统设计师只好采用更高的中频与更大的频宽、将对数据转换器与相关的频率装置需求增加,并将愈来愈高的频率模拟领域讯号转换至数字领域,以求获得摩尔定律的效益。

除了在数据转换器装置效能增益之外,使用带通取样或亚奈取样是系统的另一个关键。当此技术允许更实际的取样频率,它同时也对噪声分析以及它对数据转换器需求的影响带入额外的维度。本文最终将检视一些在决定时序装置需求,特别是抖动,必须考虑系统阶层的问题。

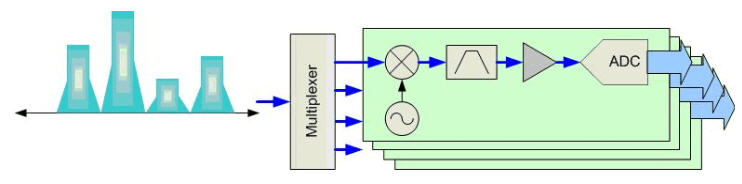

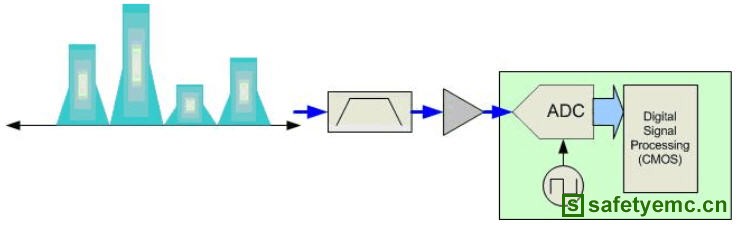

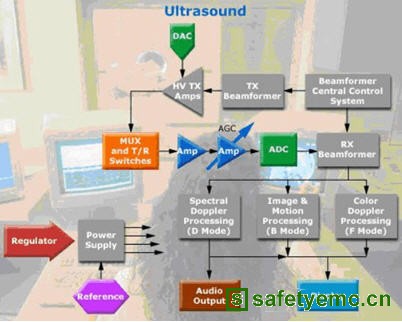

另一个明显的趋势是更高的功能性整合。在通讯领域中,如图所示在核心采用单一装置的架构,逐渐取代如图 1所示的多模块架构。不论在此架构中伴随而来的明显的技术挑战为何,其带来的效益非常吸引人:简单、灵性与高性能。

图 1 多模块架构

图2 单一、高效能 ADC 实现法 系统阶层驱动器设计

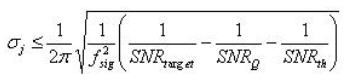

设计师熟知系统阶层对设计选择的影响,并认识到在系统中所作设计的效能所带来的影响。图 3为假设的范例,显示装置从目标系统上传串流。设计师必定了解其效能,但不一定能控制或甚至影响它。特别是当必须配合提供对ADC的界面,上传串流装置与系统会引入噪声并且变更频道特性(增益、频率响应等等)。

图 3 端点到端点之讯号路径

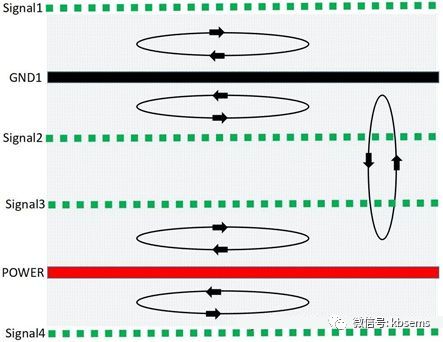

图4显示多频道讯号在数字领域的频道化。对多频道讯号进行取样,由于ADC有更高的频宽,所需的讯号的功率增加且噪声功率也增加,因此可增加其在ADC 界面的动态范围需求。多频道讯号也具有更高的峰值对平均值功率比(PAR),这表示在对单频道讯号进行取样时,一般的ADC动态范围被额外的边际消耗掉。综合上述,这些现象会增加所需ADC分辨率。由于取样流程中在ADC输入端的中频噪声的噪声混迭未受控制或未被列入考虑,亚奈取样可能对SNR有负面的影响。 最后,SNR为关键的效能指标。在取样数据系统中,设计师必须与噪声源搏斗,例如热噪声、LO相位噪声、在ADC界面上的串音与突波。在ADC内部,有噪声来源例如噪声、电源噪声、1/f 噪声、量化噪声、在取样频率上的相位噪声、量化器非线性(DNL、INL)、与交错结构、频道不匹配。在选择ADC 分辨率、取样频率、讯号处理算法时,设计师必须将上述潜在的噪声来源列入考虑。此外设计师也要设计从 ADC出发的讯号路径上传串流,设计的选择对上传串流路径的影响也必须要列为影响系统取样数据部分效能的考虑因素。

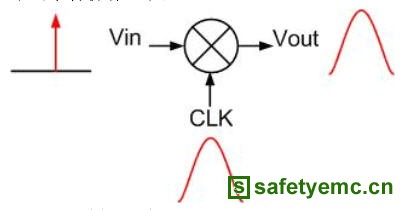

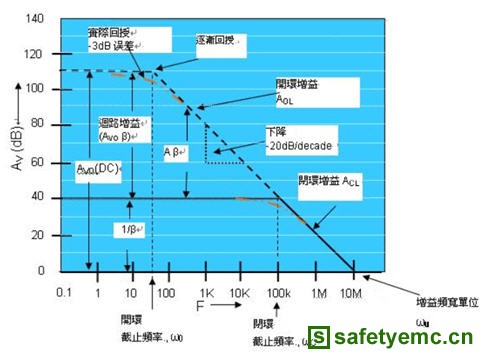

了解上传串流影响的效应是重要的,因为它们会限制设计师可用的噪声裕度。量化噪声裕度让设计师可以指定用于系统中的取样频率或数据频率所需的效能。本文第一部分讨论了取样频率相位噪声(或抖动)是如何对SNR有直接的影响(图 4)。时域上的相乘是频域上的卷积。输入端完美的正弦波(频域上的脉冲)在与其它含有噪声的正弦波混频之后会变成输出端含有噪声的正弦波,这类似ADC中的取样操作过程。

图 4 取样与混频

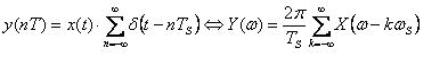

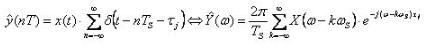

要了解相位噪声对取样频率的影响,可重新检视取样操作的数学。输入讯号,x(t)与一串完美的脉冲相乘表示理想的取样操作(图 4)。此流程产生一个取样数值的串流,y(nT),如下列公式所示。

(1)

(1)

在数学运算里,时域上的相乘与频域上的卷积为一体两面。然而,时域上理想的脉冲串可转换为频域上的脉冲串。频谱上的讯号进行卷积只会造成相似的周期性数字讯号的讯号频谱。

实际上,取样波形既非完美的脉冲,在时间上也不稳定。比较实际的做法在某个非常短的时间窗,将最后的取样电压当作输入讯号的加权平均。然而,由于关心频率抖动的影响,因此将继续使用脉冲作为取样波形,但包含了抖动项。如果频率抖动的效应有列入考虑,则脉冲函数的衰减项中会包含随机成分,tj。一般而言,tj 会以具有平均值为零与标准差为 sj的高斯(Gaussian)随机过程来建立模型。取样的讯号现在变为:

(2)

(2)

公式 2 显示输入讯号是被抖动取样函数所展开。基本上,项会造成微小、残留的频谱偏移(调变)因而将讯号频带展宽。图5显示此效应。

图5 带通取样

这里采两个步骤来描述公式 2所显示的效应。抖动项会将原始的讯号频谱进行调变,如图5(a)所示(包含取样频率)。图5(c)显示在亚奈取样之后的数字、抖动-调变的频谱。抖动对讯号频带有两个影响。

首先,抖动所造成残留的展频(由于相近的-同相位噪声 - 图5(b))直接对频带内的SNR造成劣化。其次,亚奈取样造成频带外的噪声,而混迭在讯号频带中,因此更增加噪声背景值。

在图5(c)中,「跨过」p的倍数(标为垂直的虚线)频率边界的频带外的噪声, 会反折回讯号频带。如果此频带外噪声足够高,会严重提高噪声背景值。这些复合的效应强调相近的同相位噪声与距离频率频率很大的偏移处的相位噪声的重要性。

此效应可以藉由增加取样频率作某种程度的消除,但这也会造成影像在频率上展开得更宽,而且要对需要处理的取样数量增加进行取舍。然而在某些应用上,这仍是一种可接受的取舍。此范例也强调讯号路径中的滤波以限制在 ADC 输入端的频道外噪声的重要性。

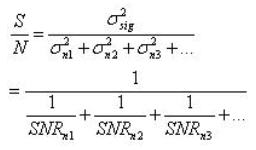

下一部分会检视如何结合数个噪声来源的效应表示为频率抖动的公式,以了解不同的来源的影响并且定义一个频率抖动上限。此范例会结合热噪声、量化噪声与取样频率相位噪声。如果假设各个这些噪声来源彼此是独立且不相关的(合理的假设),则复合的 SNR可以表示为下式:

(3)

(3)

虽然常认知的SNR是在对数单位下所表示,但注意上式的每项都是以线性单位表示的数值。在第一式中使用变异数的表示法来强调处理随机过程,它甚至可以包含所需的讯号。

为了找出各噪声源的SNR,从热噪声开始。出现在特定的固定频宽 Df 中的热噪声功率为噪声密度乘上 Df:

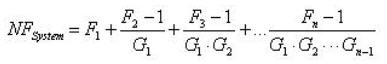

Pth-noise = N0 * Df = s2T,其中 N0 = 噪声频谱密度,单位为 W/Hz。 要在ADC输入端设定数值 N0 需要设计师进行一个端点到端点的讯号路径分析以找出系统噪声指数。参考图 3,各个次系统(接收器、讯号分配放大器、分歧器、与电缆线)具有相对应的增益与噪声指数,整合以上获得如下列公式所示的最后的系统噪声指数(关于更完整的噪声指数的讨论,请参见 [1])。

(4)

(4)

其中下标表示路径中相连接的次系统(或组件),而参数 Fn 与 Gn 为分析中所包含的各个次系统或组件的线性数值噪声指数与增益。

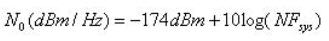

如果在讯号路径上有数个组件,让设计看起来可能相当复杂。但有一个拯救的方法是 -- 路径中第一个组件会主导最后的系统噪声指数。注意相连接的次系统或组件都列入计算中,其对噪声指数的贡献与其和上传串流次系统增益乘积成反比,也就是说,各下传串流次系统或组件对整体噪声指数具有快速削减的效应。 有经验的系统设计师了解此点,因此路径中第一个组件通常是低噪声放大器,基本上它会将系统噪声指数设定在很低的数值。因此,如果有非常大量来自ADC的讯号路径上传串流,可藉由只观察路径中前面几个次系统(组件)就可获得系统噪声指数良好的合理估计。一旦可估算 NFsys 数值,就可使用公式 5来找出ADC 输入端的噪声功率频谱密度(单位为 dBm/ Hz):

(5)

(5)

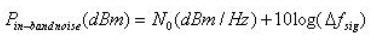

此功率频谱密度相当重要的因素有二。首先,具有宽的输入频宽的ADC可能招致动态范围损失,因为噪声功率(s2T)正比于频宽。其次,虽然基频的处理通常包含滤波器的步骤,以消除未落在所需频带内的噪声,但残留的频带内噪声对整体的SNR的计算也会有贡献。在对数单位中,噪声功率为频谱密度的对数加上所考虑的频宽取 10log的值:

(6)

(6)

要找出在所需频带中的噪声功率(单位为 dBm),取代讯号频宽为 DfBW:

(7)

(7)

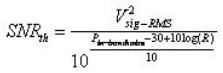

如果单位为 dBm讯号功率已知,可扣除噪声功率以获得单位为 Db的SNR 值,并将之转换为线性数值。或者可以将噪声功率转换为等效的 RMS 电压,并将 SNR 以 RMS 电压来表示:

(8)

(8)

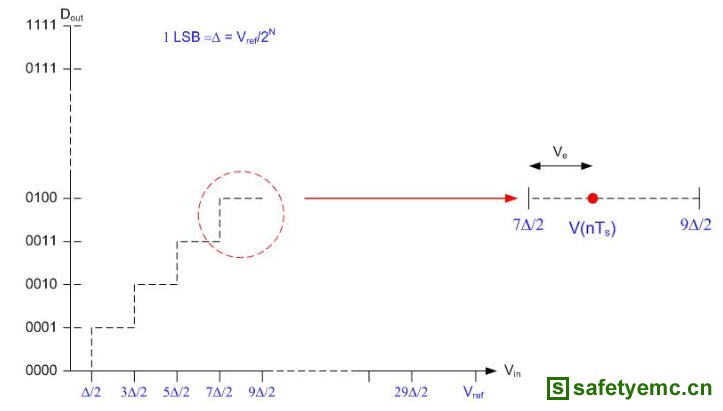

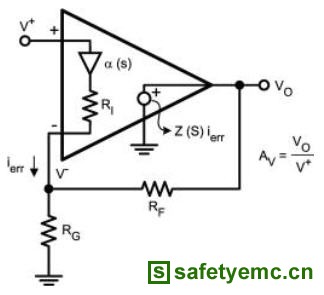

本范例中第二个噪声源为量化噪声。ADC分辨率限制会引入量化噪声(如图6所示)。图中显示一般的平移二元量化器的转换函数。水平轴表示量化器的输入电压范围,分为1 LSB的固定间隔。各个输入电压的取样值对应到这些区间中的一个。

图6 量化器模型

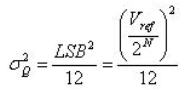

基本上,量化器将取样的电压数值无条件舍去法截取出量化区间中最接近的的整数值。在图6,任何Vin = V(nTs)落在区间 [7D/2,9D/2] 的数值会对应到数位数值 0100。如果将此数字数值转换回电压时,可能会指定一个7D/ 2 =(7/ 2)*(Vref/ 2N)的数值。实际上,真实的电压数值是更大的,因此量化器会引入误差电压,Ve。此误差项(量化噪声)可视为真实讯号数值的外加噪声。因为任何组合的输入电压数值落在特定量化区间的的分布密度是均匀的,因此误差项的分布密度项,或称为量化噪声,也是均匀的。量化噪声功率为此误差项的变异数,即:

(9)

(9)

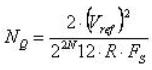

要找出关于此ADC 输入端量化噪声功率,将之除以输入电阻 R。最后,将之除以 Fs/2,可算出量化噪声功率频谱密度:

(10)

(10)

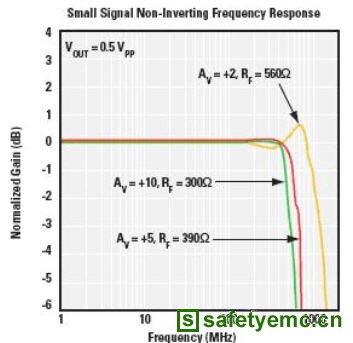

在将此项转换为对数单位dBm之后,如同热噪声一样,可计算出频带内的量化噪声功率,并使用功率值或 RMS 电压值来计算出 SNR。注意此量化噪声功率频谱密度与ADC 分辨率(N)和取样频率(FS)有反比的关系。因此,如果以RMS 电压项来表示SNR,可研究不同的分辨率与取样频率对 SNR的影响。

(11)

(11)

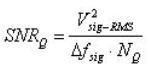

如果取样频率没有抖动,则讯号频带中(频带内)的噪声功率频谱密度会是热噪声与量化噪声的和(在此范例中)。在此情况下,最底线的 SNR 为:

(12)

(12)

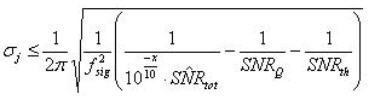

在公式 12中,设计师可以使用这些 SNR项来合成不同的参数的效应,例如取样频率与ADC 分辨率。可以研究这些参数的影响,以定义出以符合目标 SNR(或 ENOB)的边界值。在完成这样的工作尝试选择N 与 FS的数值之后,可以引入由于取样频率抖动所造成的 SNR劣化。在本文的第一部分中显示由于取样频率抖动造成的SNR 为:

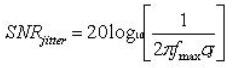

(13)

(13)

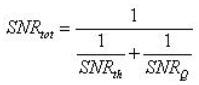

很重要的是要记住在此公式中 sj 实际上是频率RMS 抖动加上ADC 的RMS 孔径抖动的方和根(root-sum-square)值。针对由于抖动造成的SNR使用公式 13,并将之与公式 3 与 12结合,可以建立形成底限SNR的抖动与 SNR 劣化裕度的参数:

(14)

(14)

在公式 14中,x 为总 SNR 中由于抖动造成的特定可接受的劣化值(单位为 dB),fsig 为所使用的讯号的最高的频率,以及上述其它的参数。可以根据不等式来设定抖动上限。或者,只要针对特定的应用定义一个目标(最小可接受的)SNR ,并且使用修正的公式 14:

(15)

(15)

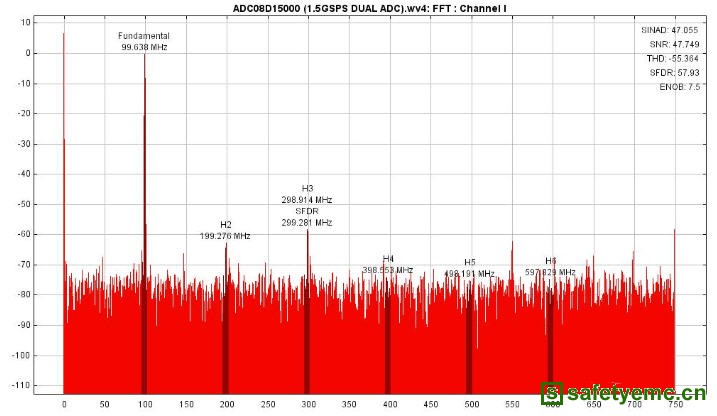

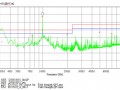

以WCDMA 系统为例,其讯号中心频率为245 MHz、频宽为5 MHz、操作在61.44 MSPS的取样频率。自动增益控制电路放在ADC 前面,设定用来对讯号功率作平均,在 ADC 输入端产生 -10 dB 全刻度的(dBFS)讯号。ADC 输入范围为 1 Vp-p,且ADC 输入端在 5 MHz 频宽中的热噪声功率设定为 -90 dBm。图7显示三种不同的 ADC 分辨率:8、10、与12 位的图形。在三种情况中,以量化噪声设定噪声背景值。各个情况中,曲线显示当抖动增加时,SNR会劣化。对于12-位 ADC而言,即使当 SNR 从 72 dB 劣化到 59 dB,最大的抖动限制仍可维持在低于 1 皮秒。

图7 抖动与SNR关系图

结论

本文讨论在使用带通取样来实现高效能多频道、数字接收器架构时,系统设计上所面临的挑战。

对于 ADC而言,要有非常高的输入频宽与高取样频率。本文中强调系统观点的设计,亦即设计选择,例如 ADC 速度与分辨率,以及取样频率需求,可由来自ADC 界面上传串流来定义系统特性。在系统的前端选择适当的低噪声放大器 (LNA),对整体噪声指数具有重大的影响,也会影响设定ADC 输入端噪声密度。

此外,低噪声取样频率的产生与分配也会主导系统的效能。由于抖动造成的取样噪声对整体 SNR 影响,因此必须搭配所有其它的噪声源造成的影响一起评估,例如热噪声与量化噪声,以决定达成所需的频带内 SNR所需的取样频率效能。

作者简介:Nicholas Gray 任职于美国国家半导体公司数据转换系统部应用工程师,电子邮件:nicholas.gray@nsc.com

苏公网安备32050802011615号

苏公网安备32050802011615号