提供双向、实时数据传输的USB接口,以其即插即用、可热插拔和价格低廉等优点,目前已成为计算机和信息电子产品连接外围设备的首选接口。时下流行的USB2.0具有高达480Mbps的传输速率,并与传输速率为12Mbps的全速USB1.1和传输速率为1.5Mbps的低速USB1.0完全兼容。这使得数字图像器、扫描仪、视频会议摄像机等消费类产品可以与计算机进行高速、高性能的数据传输。另外值得一提的是,USB2.0的加强版USB OTG可以实现没有主机时设备与设备之间的数据传输。例如。数码相机可以直接与打印机连接并打印照片,PDA可以与其它品牌的PDA进行数据传输或文件交换。

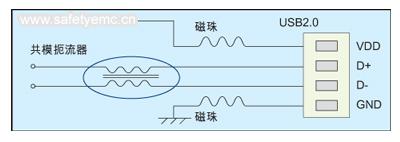

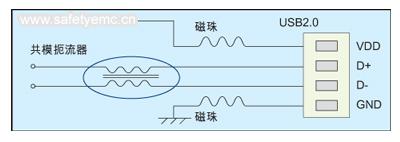

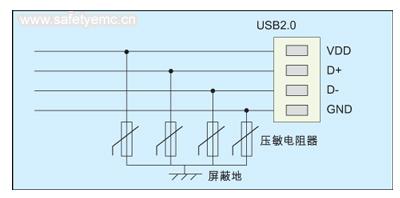

图 1:USB2.0的噪声抑制电路图

USB接口的传输速率很高,因此如何提高USB信号的传输质量、减小电磁干扰(EMI)和静电放电(ESD)成为USB设计的关键。本文以USB2.0为例,从电路设计和PCB设计两个方面对此进行分析。

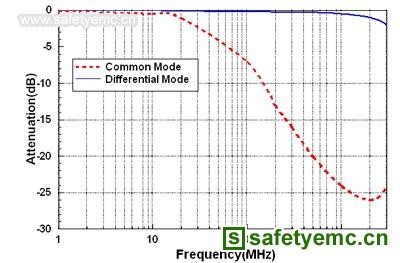

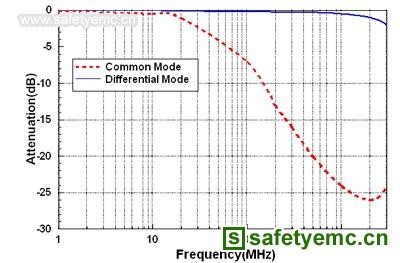

图2:SDCW2012-2-900的衰减频谱

当USB2.0接口采用高速差动信号传输方式时,由于接地层与电源层的信号摇摆,放射噪声会有所增加。因此,为避免串扰并保证信号的完整性,消除将要混入高速信号中的共模噪声是电磁兼容设计的必要对策。在图1所示的电路中,数据电源线和地线上分别串联一个阻抗为120欧姆、额定电流为2A的磁珠,而差分线对上则串联一个共模阻抗为90欧姆的共模扼流器。共模抗流器由两根导线同方向绕在磁芯材料上,当共模电流通过时,共模抗流器会因磁通量叠加而产生高阻抗;当差模电流通过时,共模抗流器因磁通量互相抵消而产生较小阻抗。以深圳顺络电子有限公司生产的共模抗流器SDCW2012-2-900为例,该器件在100MHz的差模阻抗仅为4.6欧姆。从图2所示的衰减特性也能看出共模扼流器对差分信号不会造成影响,主要是针对共模电流进行选择性的衰减。

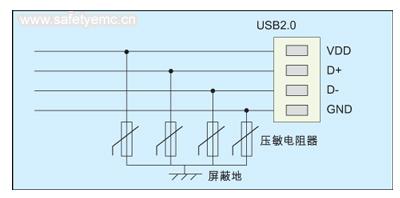

图3:USB2.0的ESD防护电路图

由于USB接口具有可热插拔性,USB接口很容易因不可避免的人为因素而导致静电损坏器件,比如死机、烧板等。因此使用USB接口的用户迫切要求加入防ESD的保护器件。在图3电路中,数据电源线、地线上各有一个工作电压为5.5V、电容为100pF的压敏电阻连到屏蔽地上。差分线对因数据传送速度高达480Mbps,则需要连接电容小于4pF的器件,因为较大的电容可导致数据信号波形恶化,甚至出现位错误。因此在差分线对上接入工作电压为18V、电容最大值为4pF的压敏电阻器。图4所示的电压波形也验证了电容为4pF的压敏电阻器(如深圳顺络电子有限公司生产的SDV1005H180C4R0GPT)对波形的影响不大。

对于USB2.0的PCB布线,需要考虑以下原则:

图4:不同电容值的压敏电阻对波形的影响

1.差分线对要保持线长匹配,否则会导致时序偏移、降低信号质量以及增加EMI;2.差分线对之间的间距要保持小于10mm,并增大它们与其它信号走线的间距;3.差分走线要求在同一板层上,因为不同层之间的阻抗、过孔等差别会降低差模传输的效果而引入共模噪声;4.差分信号线之间的耦合会影响信号线的外在阻抗,必须采用终端电阻实现对差分传输线的最佳匹配;5.尽量减少过孔等会引起线路不连续的因素;6.避免导致阻值不连续性的90度走线,可用圆弧或45度折线来代替;7.压敏电阻器的接地端要接入屏蔽地层,并放置在端口位置。

ESD保护二极管选型详解

ESD(静电放电)保护二极管的选型核心在于 “因势利导” :为正常信号提供“无阻力”通路,为异常ESD脉冲提供“低阻力”的泄放通路。选型过程就是围绕这一核心,匹配电路需求与二极管参数的过程。一、明确被保护对象

0评论2025-09-23100

静电放电测试标准讲解及解析

在现代电子设备的设计与生产中,静电放电(Electrostatic Discharge,ESD)是一个不容忽视的重要问题。静电放电不仅能够直接损坏敏感的电子元件,导致系统故障,还可能因静电累积导致性能不稳定、数据丢失等严重后果

1评论2025-06-07548

静电放电测试标准——理解和比较差异

人体模型 (HBM) 器件级测试是 ESD 测试常用的模型。它用于表征电子元件对 ESD 损坏的敏感性。该测试模拟人体对电子元件的放电,如果人体积累了残余电荷(例如,穿着袜子拖着脚走过地毯)并触摸电子设备,就会发生这

0评论2025-03-23308

电路级静电防护设计技巧与ESD防护方法

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用

3评论2021-01-28796

电路保护的意义是什么?常用的器件有哪些?

电子电路很容易在过压、过流、浪涌等情况发生的时候损坏,随着技术的发展,电子电路的产品日益多样化和复杂化,而电路保护则变得尤为重要。电路保护元件也从简单的玻璃管保险丝,变得种类更多,防护性能更优越。电路

1评论2020-10-19267

手机开发过程中 预防ESD失效的方法

现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁骚扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、电路及接口电路造成的破坏等问题越来越引起人们的重视。目前手机的功能越

0评论2018-12-25424

解析PCB板设计中抗ESD的常见防范措施

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件

2评论2018-12-25566

如何提高隔离接口模块的ESD抗扰能力?

隔离模块应用于各类复杂的工业环境中,以提升总线的抗干扰能力,但设备接口可能会采用端子与外部连接,可能会在安装、维修过程中有静电等能量输入,从而导致隔离模块损坏。那么该如何避免这样的问题呢?本文为您揭秘

0评论2018-07-02859