PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。

电路环路

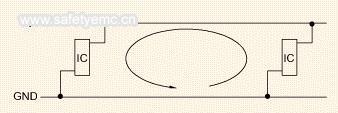

电流通过感应进入到电路环路,这些环路是封闭的,并具有变化的磁通量。电流的幅度与环的面积成正比。较大的环路包含有较多的磁通量,因而在电路中感应出较强的电流。因此,必 须减少环路面积。

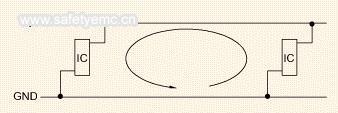

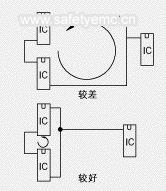

最常见的环路如图1所示,由电源和地线所形成。在可能的条件下,可以采用具有电源及接地层的多层PCB设计。多层电路板不仅将电源和接地间的回路面积减到最小,而且也减小了ESD脉冲产生的高频EMI电磁场。

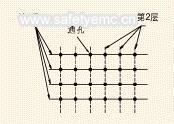

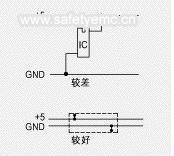

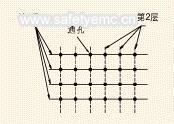

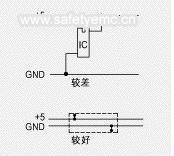

如果不能采用多层电路板,那么用于电源线和接地的线必须连接成如图2所示的网格状。网格连接可以起到电源和接地层的作用,用过孔连接各层的印制线,在每个方向上过孔连接间隔应该在6厘米内。另外,在布线时,将电源和接地印制线尽可能靠近也可以降低环路面积,如图3所示。

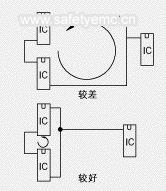

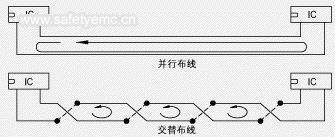

减少环路面积及感应电流的另一个方法是减小互连器件间的平行通路,见图4。

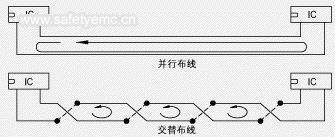

当必须采用长于30厘米的信号连接线时,可以采用保护线,如图5所示。一个更好的办法是在信号线附近放置地层。信号线应该距保护线或接地线层13毫米以内。

如图6所示,将每个敏感元件的长信号线(>30厘米)或电源线与其接地线进行交叉布置。交叉的连线必须从上到下或从左到右的规则间隔布置。

电路连线长度

长的信号线也可成为接收ESD脉冲能量的天线,尽量使用较短信号线可以降低信号线作为接收ESD电磁场天线的效率。

尽量将互连的器件放在相邻位置,以减少互连的印制线长度。

ESD保护二极管选型详解

ESD(静电放电)保护二极管的选型核心在于 “因势利导” :为正常信号提供“无阻力”通路,为异常ESD脉冲提供“低阻力”的泄放通路。选型过程就是围绕这一核心,匹配电路需求与二极管参数的过程。一、明确被保护对象

0评论2025-09-2398

静电放电测试标准讲解及解析

在现代电子设备的设计与生产中,静电放电(Electrostatic Discharge,ESD)是一个不容忽视的重要问题。静电放电不仅能够直接损坏敏感的电子元件,导致系统故障,还可能因静电累积导致性能不稳定、数据丢失等严重后果

1评论2025-06-07539

静电放电测试标准——理解和比较差异

人体模型 (HBM) 器件级测试是 ESD 测试常用的模型。它用于表征电子元件对 ESD 损坏的敏感性。该测试模拟人体对电子元件的放电,如果人体积累了残余电荷(例如,穿着袜子拖着脚走过地毯)并触摸电子设备,就会发生这

0评论2025-03-23302

电路级静电防护设计技巧与ESD防护方法

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用

3评论2021-01-28793

电路保护的意义是什么?常用的器件有哪些?

电子电路很容易在过压、过流、浪涌等情况发生的时候损坏,随着技术的发展,电子电路的产品日益多样化和复杂化,而电路保护则变得尤为重要。电路保护元件也从简单的玻璃管保险丝,变得种类更多,防护性能更优越。电路

1评论2020-10-19266

手机开发过程中 预防ESD失效的方法

现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁骚扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、电路及接口电路造成的破坏等问题越来越引起人们的重视。目前手机的功能越

0评论2018-12-25423

解析PCB板设计中抗ESD的常见防范措施

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件

2评论2018-12-25564

如何提高隔离接口模块的ESD抗扰能力?

隔离模块应用于各类复杂的工业环境中,以提升总线的抗干扰能力,但设备接口可能会采用端子与外部连接,可能会在安装、维修过程中有静电等能量输入,从而导致隔离模块损坏。那么该如何避免这样的问题呢?本文为您揭秘

0评论2018-07-02857