在人们的日常工作生活中,静电放电(ESD)现象可谓无处不在,瞬间产生的上升时间低于纳秒(ns)、持续时间可达数百纳秒且高达数十安培的电流,会对手机、笔记本电脑等电子系统造成损伤。

对于电子系统设计人员而言,如果没有采取适当的ESD保护措施,所设计的电子产品就会有遭到损伤的可能。因此,电子系统设计中的一项重要课题便是确保使其能够承受ESD的冲击,并继续正常工作。

ESD保护方法

为了给电子系统提供ESD保护,可以从不同的角度来着手。一种方法是在半导体芯片内建ESD保护架构。不过,日趋缩小的CMOS芯片已经越来越不足以承受进行内部2 kV等级的ESD保护所需要的面积。安森美半导体标准产品部亚太区市场营销副总裁麦满权指出:真正有效的ESD保护是不能完全集成到CMOS芯片之中的!

其次,也可以在物理电路设计方面下功夫,较敏感的电路元件应该尽量远离通孔或接缝处,如果可能的话,线缆连接器的接地应该要在系统信号引脚接触前先连接到系统的接地,通过这样的方式,线缆上所发生的放电事件就比较不会造成干扰或破坏。

此外,软件也能够为ESD设计作出贡献。系统连接的感测器比较容易受到ESD的冲击,造成接口电路的锁住情况,而能够感测锁住情况的软件则可以用来重置接口电路且无须操作人员的接入。

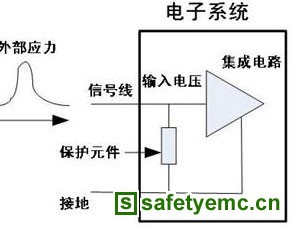

不过,总是有部分电路点较为敏感,同时也很难与外部隔离。因此,最有效的方法是使用保护元件来将电流导离较敏感的元件。也就是在电子系统的连接器或端口处放置ESD保护元件,使得电流流经保护元件,且不流经敏感元件,以维持敏感元件的低电压,使其免受ESD应力影响,进入有效控制ESD事件的发生,如图1所示。当然,合格的ESD元件必须具有低泄漏和低电容,且在多重应力作用下功能不下降,从而不降低电路的功能。

图1:典型的ESD保护元件应用电路图

常见ESD保护元件分类

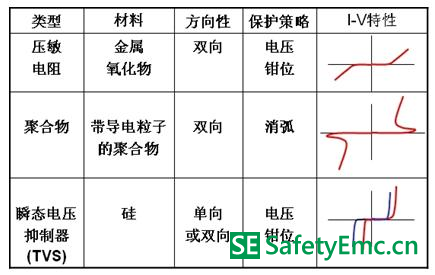

安森美半导体来自美国的ESD保护专家Robert Ashton博士说,一般而言,ESD保护元件的分类可以通过其保护策略与方向性来进行,主要包括压敏电阻、聚合物和瞬态电压抑 制器(TVS)等,如表1所示。在这几种保护元件中,压敏电阻在低电压时,呈现出高电阻,其中的每个小型二极管两端的电压都相当低,同时电流也相当小;而在较高电压时,其中的独立二极管开始导通,同时压敏电阻的电阻会下降。从表1中我们也可以看出压敏电阻为双向保护元件。而对于带导电粒子的聚合物而言,在正常电压下,这些材料拥有相当高的电阻,但当发生ESD冲击时,导电粒子间的小间隙会成为突波音隙阵列,从而带来低电阻路径。

瞬态电压抑制器(TVS)则为采用标准与齐纳二极管特性设计的硅芯片元件。TVS元件主要针对能够以低动态电阻承载大电流的要求进行优化,由于TVS元件通常采用集成电路(IC)方式生产,因此我们可以看到各种各样的单向、双向及以阵列方式排列的单芯片产品。

表1:常见ESD保护元件分类

利用屏幕截图和TLP进行ESD保护元件的大电流性能鉴定

Ashton博士说在正常工作条件下,ESD保护元件应该保持在不动作状态,同时不会对电子系统的功能造成任何影响,这可以通过维持低电流以及足以在特定数据传输速率下维持数据完整性的低电容值来达成。而在ESD应力冲击或者说大电流冲击条件下,ESD保护元件的第一个要求就是必须能够正常工作,要有够低的电阻以便能够限制受保护点的电压;其次,必须能够快速动作,这样才能使上升时间低于纳秒的ESD冲击上升时间。

众所周知,对于电子系统而言,它必须能够在IEC 61000-4-2标准测试条件下存续。虽然大部分的ESD保护元件都宣称能够承受IEC 61000-4-2所指定的应力冲击等级,如8 kV或第四级(Class 4),但业界却没有公认的ESD保护元件大电流抑制特性测试的合格标准。对此,安森美半导体给出了自己的定义,也就是在±10 kV应力电压 (高于8 kV)测试下,被测器件仍然符合其数据表规范,且器件特性没有显著变化。

不过,要比较不同ESD保护元件的大电流抑制特性,还需要对其进行测试鉴定。而通过对不同ESD保护元件施加大电流冲击所产生的波形的屏幕截图对比,是重要的第一步。

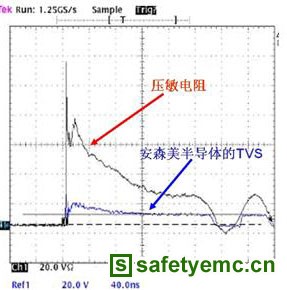

图3: TVS元件与压敏电阻在8kV IEC 61000-4-2应力冲击测试下的输出波形对比

图3的屏幕截图就是这样一个范例。从图中可以看出,安森美半导体的TVS元件可以迅速将ESD应力降低,即从8 kV静电电压钳位到5至6 V的水平;但压敏电阻的曲线则下降得很慢,而且无法降到很低的水平。该曲线表明,TVS器件的恢复时间非常短,经过TVS器件泄漏到后面电路的能量也非常少,特别适合于便携式设备的应用。

而在多重应力条件下,两者的差别就表现得更为突出。由于TVS采用二极管工作原理,受到电击后,会立即击穿,然后关闭,对器件没有损伤,因此可以说没有寿命限制。对于压敏电阻而言,它采用的是物理吸收原理,每经过一次ESD事件,材料就会受到一定的物理损伤,形成无法恢复的漏电通道;而且,要达到更好的吸收效果,就要使用更多的材料,使其体积增加,进而限制了在今天小型化产品当中的应用。

有鉴于此,安森美半导体标准产品部亚太区市场营销副总裁麦满权先生打了一个比方,也就是在ESD保护方面,压敏电阻保护施展的是“少林功夫”,用“身体(压敏电阻)”去硬扛,会让自己“很受伤”,而TVS耍的是“太极拳”,在ESD应力冲击IC之前,就将冲击力给“引导开”或“消减掉”。

两相对比,其结果是在施加1,000次8kV IEC 61000-4-2 ESD脉冲条件下,安森美半导体的TVS元件的漏电流小于0.1 µA,而压敏电阻在少于20个ESD脉冲下漏电流就会超过100 µA。由此可见,在重复ESD应用作用下,TVS仍能维持极高的性能,而压敏电阻的性能会随之下降,聚合物也面临着跟压敏电阻类似的问题。

不过,用示波器对不同保护元件在ESD应力冲击测试下的大电流抑制特性或者说是I-V曲线进行屏幕截图对比也存在不足之处。首先便是这种屏幕截图上的V(t)与I(t)的变化非常复杂,且并不能测量击穿电压、维持电压、维持电流以及二次击穿电流等基础参数,而通过对这些参数的分析可以找到电路设计和工艺的弱点。

图4:时域反射(TDR) TLP测试的结构示意图

在这种情况下,采用传输线路脉冲(TLP)方法就是很好的下一步。所谓的TLP测试,就是一种利用矩形短脉冲(50~200 ns)来测量ESD保护元件的电流-电压特性曲线的方法。这个短脉冲用来模拟作用于保护元件的短ESD脉冲,而恒定阻抗的传输线路可以生成恒定幅度的方波。

TLP测试通过方波测试脉冲加到待测器件(DUT)的两个引脚之间进行测试。TLP测试前要先对电路中的传输线路充电,测试时将被测器件接入,传输线路通过被测器件放电。改变电路和输入电压和传输线路的长度可以模拟在不同能量中的ESD脉冲,从而得到器件的ESD大电流抑制能力。TLP测试先从小电压脉冲开始,随后连续增加直到获得足够多的数据点,以作出完整的I-V曲线。通常测试脉冲的幅度会加大到使DUT彻底损伤为止,作而获得其精确的允许最大脉冲电流。

总的来看,ESD保护元件的TLP测试方法优势突出,不仅可以确认屏幕截图数据,还可用于解析ESD保护元件的基础参数,非常适用于对不同保护元件进行对比。

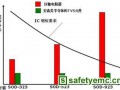

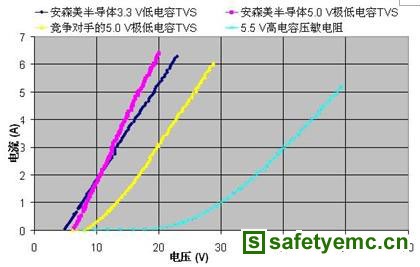

图5:不同ESD保护元件的TLP测试I-V曲线

结合ESD脉冲测试和TLP测试,我们可以得出结论,在不同ESD保护元件中,TVS元件,特别是安森美半导体的TVS元件的大电流导电率极佳,且在重复应力条件下仍能维持优异性能,不存在压敏电阻或聚合物那样的使用增多后会出现性能下降的问题;至于其在电容方面的不足,也随着新的低电容设计的出现,而消除了早前的大电容问题。

不同便携应用的ESD保护解决方案

按照TVS电容与传输速率的不同,安森美半导体将便携应用的ESD保护元件市场划分为三个区域。第一是标准ESD保护,满足大功率(高于100瓦)、最低钳位电压要求,适用于键区、按钮、电池接头、充电器接口、旁键等的保护,TVS电容在1,000 pF至100 pF之间;在这方面,安森美半导体有ESD5Z5、ESD9X等单向通用TVS产品。

第二是高速ESD保护,要求数据传输率更快、低电容,应用于USB1.1、USB2.0FS、FM天线、SIM卡和音频线路等,TVS电容在40 pF至5 pF;在这方面,安森美半导体提供了ESD9C和ESD7C等单向TVS、ESD5B和ESD9B双向TVS、NUP4202和NUP2202等单向ESD保护阵列,以及NUP4xV、NUP8010和NUP5120等双向ESD保护阵列。

第三个是超高速ESD保护,如USB2.0HS、HDMI、RF天线等,TVS电容在5pF以下,电容值与钳位相反,不可用传统TVS技术。这方面,客户可以选择安森美半导体的ESD9单向TVS(电容小于2 pF)、ESD11和ESD9双向TVS(电容小于0.5 pF)、NUP4212和NUP8012单向ESD保护阵列,以及NUP4214双向ESD保护阵列。

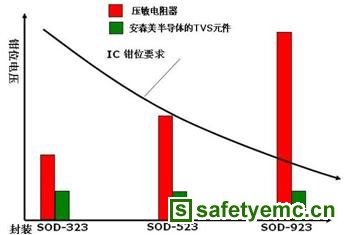

图6:多层压敏电阻(MLV) 与安森美半导体的TVS硅芯片技术发展趋势对比

安森美半导体的ESD保护解决方案拥有众多优势,如领先业界的超小封装、符合各种规范及标准的优异性能、可靠的质量及更长的使用寿命等;此外,安森美半导体还不断研发,以提供更先进的ESD保护解决方案。

总结

要对电子系统进行ESD保护设计,最有效的方法还是在连接器和端口处放置外部保护元件。在压敏电阻、聚合物和TVS这几种常见保护元件中,前两者分别在经济性和低电容方面占有优势,但TVS则拥有极佳的导电率,并且在多重应用作用下仍能维持强劲性能。安森美半导体提供一系列采用先进封装、拥有极佳性能的TVS元件,分别面向大功率、高速率和超高速率等应用领域,全方面满足客户的高性能ESD保护需求。