IC内部保护电路

标准保护方案是限制到达IC核心电路的电压和电流。图1所示保护器件包括:

·ESD二极管:在引脚与电源之间提供一个低阻通道。

·电源钳位:连接在电源之间,正常供电条件下不汲取电流,出现ESD冲击时呈低阻。

ESD二极管

二极管连接在测试引脚和电源之间,为ESD电流提供低阻路径。

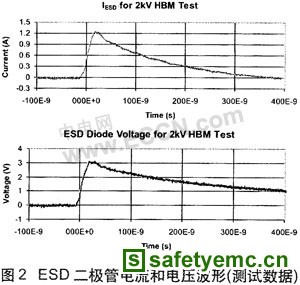

如果对IC进行HBM测试,测试电路的初始电压是2kV,ESD电流约为1.33A:

IESD=2kV/1.5kΩ±10%

大电流在ESD二极管和引线上产生I-R压降,该电压高于二极管本身的压降。IC可靠性报告中给出了器件设计所能承受的ESD测试电压。

电源钳位

引脚之间需要为ESD电流提供低阻路径,包括电源引脚。钳位电路在正常工作状态下呈现为高阻抗。

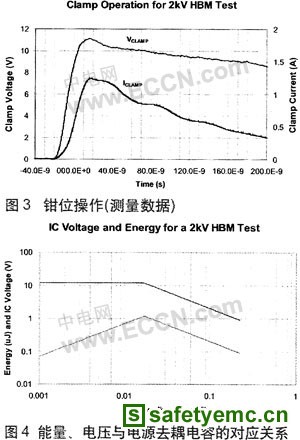

双极性IC的钳位操作类似于在受保护核电路中受冲击时呈现击穿状态,钳位晶体管的过压导致集电极-基极之间的雪崩电流,发射结的正向偏置会进一步提高集电极电流,导致快恢复状态。

钳位二极管在IC其它电路遭到破坏之前导通,二极管要有足够的承受力,保证ESD电 流不会导致二次击穿。

ESD保护和应用电路

电源去耦电容会影响钳位操作,钳位二极管在低于绝对额定电压的正常供电情况下呈现高阻抗。电荷传递到去耦电容可能产生高于IC额定电压的电平,但还不足以使二极管导通。此时,电容相当于一个能源,迅速将能量释放到IC。

对于一个给定的去耦电容,ESD测试中初始电压的变化遵循电荷守恒。例如,使用一个0.01μF去耦电容,2kV HBM测试电压可以达到20V。

V1=VESD×C0/(C0+C1)或20V=2kV×100pF/(100pF+0.01μF)

被保护引脚电容上的能量如图4所示,对小的去耦电容,钳位二极管通过进入快恢复模式限制V1。电容越大,能量越大。

钳位电压高于器件所能承受的电压(典型值6V),低于二极管的快恢复电压(~10V),对于存在去耦电容的情况,由于电容储能可能导致某些问题。如果器件在没有外部电路的情况下进行测试,10V电压是可以接受的,对器件不会构成威胁。

静电放电测试标准讲解及解析

在现代电子设备的设计与生产中,静电放电(Electrostatic Discharge,ESD)是一个不容忽视的重要问题。静电放电不仅能够直接损坏敏感的电子元件,导致系统故障,还可能因静电累积导致性能不稳定、数据丢失等严重后果

1评论2025-06-07185

静电放电测试标准——理解和比较差异

人体模型 (HBM) 器件级测试是 ESD 测试常用的模型。它用于表征电子元件对 ESD 损坏的敏感性。该测试模拟人体对电子元件的放电,如果人体积累了残余电荷(例如,穿着袜子拖着脚走过地毯)并触摸电子设备,就会发生这

0评论2025-03-23159

电路级静电防护设计技巧与ESD防护方法

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用

3评论2021-01-28659

电路保护的意义是什么?常用的器件有哪些?

电子电路很容易在过压、过流、浪涌等情况发生的时候损坏,随着技术的发展,电子电路的产品日益多样化和复杂化,而电路保护则变得尤为重要。电路保护元件也从简单的玻璃管保险丝,变得种类更多,防护性能更优越。电路

1评论2020-10-19212

手机开发过程中 预防ESD失效的方法

现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁骚扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、电路及接口电路造成的破坏等问题越来越引起人们的重视。目前手机的功能越

0评论2018-12-25368

解析PCB板设计中抗ESD的常见防范措施

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件

2评论2018-12-25498

如何提高隔离接口模块的ESD抗扰能力?

隔离模块应用于各类复杂的工业环境中,以提升总线的抗干扰能力,但设备接口可能会采用端子与外部连接,可能会在安装、维修过程中有静电等能量输入,从而导致隔离模块损坏。那么该如何避免这样的问题呢?本文为您揭秘

0评论2018-07-02790

共享单车电子锁的防静电保护方案

全民共享,共享经济,互联网+,这些热点关键词不是说说而已。在基础公共建设比如:公路,铁路,大桥,隧道,公园已经建设完整后。我们的社会开始建设移动共享经济比如:共享自行车,共享电动自行车,共享电动汽车,共

1评论2017-08-18855