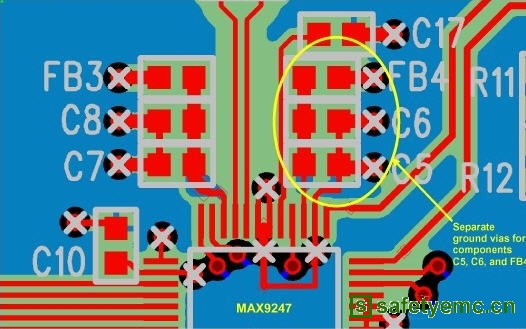

●考虑每个接地点都采用了多个过孔,过孔的寄生电感是造成非理想特性的关键。采用多个过孔有助于减小电感,从而提高性能。

●对IC的电源端进行旁路非常重要,特别是对于SerDes系统。类似于接地的考虑,电源引脚从电源侧看必须具有低交流阻抗,尤其是低压差分信号(LVDS)线路、I/O电源引脚以及用于锁相环(PLL)电路的电源引脚。建议每个引脚连接两个旁路电容,这两个电容通常相差10倍至100倍(例如0.1?F和1nF)。最小电容应距离需要去耦/旁路的电源引脚最近。

●可以考虑在SerDes系统的电源引脚使用磁珠,特别是LVDS线路、I/O电源引脚和PLL电源引脚,当然,这一点适用于所有电源引脚。磁珠有助于减小高频能量的输入和输出,选择峰值阻抗为100Ω至600Ω、额定值至少为100mA的磁珠。

图1所示为MAX9247串行器PCB的放大图片,关键元件有FB4、C6和C5,这些元件被布置在一列,丝印参考点位于各自元件外框的右侧。图1底部为MAX9247的一角。FB4的右侧端子通过一个过孔连接到嵌入式接地区域。FB4的左侧端子向下连接至C6和C5,然后连接至MAX9247的引脚27,这是串行器的V*LL电源节点。注意,连接FB4、C5和C6的引线较宽,使寄生电感降至最低。由于该引线为了满足MAX9247的引脚焊距而变窄,所以在C5和MAX9247之间使用了一个多边形覆铜,保持尽量宽的引线,同时尽量靠近串行器。而且,C5和C6的接地显示每个电容自身都具有连接至接地区域的过孔(每个元件的右侧)。最上层覆铜区域为接地层,为C6和C5至MAX9247的引脚26提供直接的低电感连接通路,该引脚为串行器的PLLGND。

图1. MAX9247的推荐旁路和接地设计

关于串行器的建议

抑制串行器的EMI辐射需要了解一些基本概念。通常情况下,串行器对EMC测试不是特别敏感;然而,其输出需要具有阻抗固定的平衡传输线对。大多数串行器IC针对100Ω阻抗进行优化。如果设计中有不可更改的设计因素,接近该范围的其它阻值也可以接受。如果串行器输出需要连接到机箱以外,并入汽车线束,这些输出就必须能够承受对电池短路故障。最简单的解决方案是采用0.1?F电容对每路输出进行交流耦合。然而,这样需要一个直流平衡串行器,例如MAX9209、MAX9217或MAX9247。也可以使用非直流平衡器件,但系统设计必须保证所需偏压由外部提供,而这通常不可行。最后,在串行器输出接出PCB之前,输出端往往连接一个共模扼流圈。这对串行器套件之外的共模噪声抑制有一定保护作用。当然,共模扼流圈的作用很有限,当插入损耗(标称为1dB)影响到链路的可靠性时,则不应使用。