在今年计算机硬件的热门话题中,USB3.0绝对是最受瞩目的。自从2000年USB2.0出来后,这项应用已深植各项电子产品中,在各式各样的接口规格中, USB应可算是使用最广泛的了。USB3.0的数据传输速率比现有的USB2.0快上十倍,刚好迎合日益大增的高画质、大容量储存需求。无论是外接式硬盘、随身碟、相机记忆卡均可大幅缩减储存的时间。除了在计算机上的应用之外,手机与相机的传输也几乎都是使用USB规格,甚至许多产品更直接把充电端与USB结合,难怪各界皆如此期待USB3.0的广泛使用,好让用户享受4.8Gbps的传输快感。USB3.0接口分成主机(Host)端与装置(Device)端,必须先有Host端的支持,周边的Device端才能搭配;而芯片大厂英特尔及超威自2010年起亦已开始研发将支持USB3.0为南桥规格,加上微软Windows 7也确定研发支持USB3.0的drivers,预估USB 3.0取代USB2.0已是既定趋势。

为实现十倍于USB2.0的传输速度,USB 3.0控制IC必须使用更先进的制程来设计与制造,但这也造成USB 3.0的控制IC对ESD的耐受能力快速下降。除此之外,USB 3.0会被大量用来传输影音数据,对数据传输容错率会有越严格的要求,使得使用额外的保护组件来防止ESD事件对数据传输的干扰变得很必要。除了传输速度的要求之外,另一个用户最普遍的USB应用就是即插即用、随拔即关。然而这个热插入动作却也经常是造成电子系统工作异常、甚至造成USB端口组件毁坏的元凶,因为如静电放电(ESD)等瞬时噪声就是来自这个热插入动作。

要用在USB3.0端口的ESD防护组件必须同时符合下面三项要求:

第一、ESD防护组件本身的寄生电容必须要小,为不影响USB3.0 4.8Gbps的传输速率,其寄生电容必须小于0.3pF。

第二、防护组件对ESD的耐受能力必须要高,最少要能承受IEC 61000-4-2接触模式8kV ESD的轰击。

第三、也是最重要的一项要求,防护组件在ESD事件发生期间所提供的箝制电压必须要够低,不能造成传输数据的损坏。

以上三项要求缺一不可,缺少了任何一个要项,USB3.0端口就无法被完善地保护。然而要同时符合以上三项要求的ESD防护组件,其本身的设计难度就相当高。

晶焱科技拥有先进的ESD防护设计技术,特别针对USB3.0的防护需求,推出AZ1065系列的ESD防护组件。为避免防护组件的寄生电容影响USB3.0 4.8Gbps差动(Differential)讯号的高速传输,AZ1065的寄生电容已低于0.3pF。在极低的电容特性下,任一接脚在室温时仍皆可承受IEC 61000-4-2接触模式10kV ESD的轰击。最重要是,以相同寄生电容来比较,AZ1065拥有最低的ESD箝制电压,可有效防止数据传输时被ESD事件所干扰,才能让拥有USB 3.0端口的电子系统有机会通过Class-A的IEC 61000-4-2系统级静电放电保护测试。利用传输线脉冲系统(TLP)测量AZ1065后,可以观察到如图一的ESD箝制电压特性。在IEC 61000-4-2接触模式6kV的ESD冲击下(TLP电流等效约为17A),箝制电压仅有13.4V,将得以有效避免系统产品于静电测试时发生数据错误、当机甚至损坏的情况。

图1:AZ1065-06F的ESD箝制电压测试曲线。

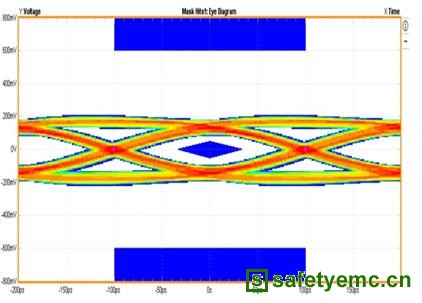

在电子产品的USB3.0应用中,AZ1065-06F将是静电放电防护的最佳解决方案。图2所示即为装有ESD防护组件AZ1065-06F的USB3.0端口顺利通过5Gbps的Eye Diagram测试结果。

图2:AZ1065-06F 5Gbps的Eye Diagram测试结果。

在电子产品朝向轻薄短小的发展趋势下,产品的印刷电路板(PCB)也随之越来越小,但在产品功能强大的要求之下,线路也变得更加复杂,因此PCB的面积已变得寸土寸金,造成产品设计时相当大的困扰。AZ1065系列产品提供六个极低电容的接脚,可同时保护USB3.0的两组差动对(TX and RX)及USB2.0的差动对(D+ and D-),具有缩小PCB面积与降低布局(Layout)复杂度等优点,可节省系统成本。更特别的是AZ1065-06F首先采用交错型式的接脚,以提供PCB Layout时可利用穿透式(Feedthrough)的设计,图3即为AZ1065-06F的接线方式。此种首创的组件接脚方式将可免除绕线时的诸多困扰,不但对缩短产品设计时间的PCB Layout工作有相当大的帮助,同时差动讯号线的Layout也将更为对称,减少讯号传输错误的机会。

图3:以AZ1065-06F作为USB3.0 ESD防护,线路可利用穿透式Layout达成。