抗 EFT 能力

IEC61000-4-4的系统级测试标准被称为电快速瞬变(EFT)抗扰度测试模型(图10)。 EFT 抗扰度测试模拟日常环境中因关闭感性负载、继电器触点弹跳以及直流或通用电机运行而导致的瞬态。该测试对所有电源线、信号线和地线进行。这也称为突发抗扰度测试。

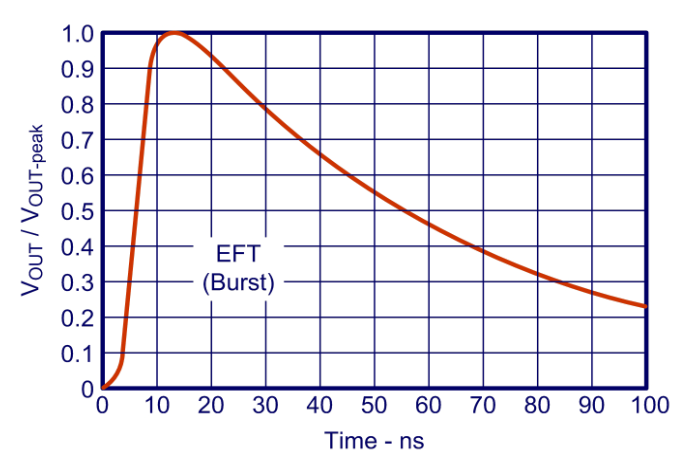

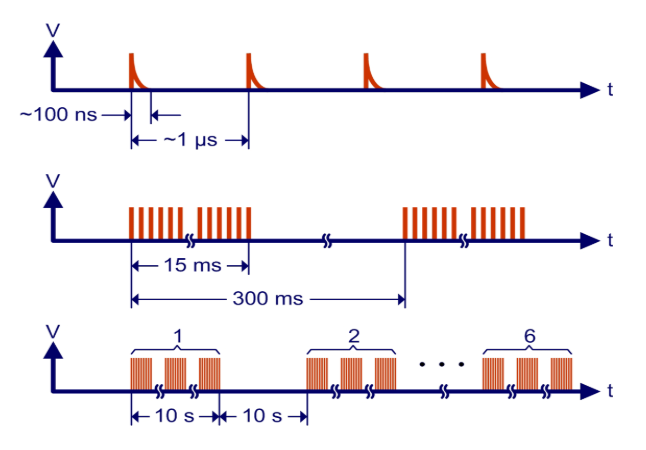

突发被定义为具有有限持续时间的脉冲序列。在 EFT/突发抗扰度测试中,突发发生器产生一系列测试脉冲,在不到 100 ns 的时间内衰减至其峰值的 50%。下一个相邻脉冲通常是 1 ?s 后。典型的突发持续时间为 15 ms。突发周期,即从一个突发开始到下一个突发的时间,为 300 ms。该循环重复 10 秒,之后 10 秒不进行测试。这代表一个测试周期。

此操作必须重复总共 6 次,总时间为 110 秒。 EFT/突发脉冲群抗扰度测试的重要性在于其脉冲上升时间短、重复率高以及能量含量低。

虽然 EFT 的快速上升时间和低能量含量与 ESD 脉冲有些相似,但每个测试周期的脉冲数量却并非如此。假设脉冲前沿之间的间隔为 1 μs,则持续时间 15 ms 的 EFT 突发至少包含 15000 个脉冲。乘以 10 秒窗口内的突发数量,即 10 秒 / 300 毫秒 = 33.3 突发,每 10 秒窗口产生 500,000 个脉冲。因此,应用六个具有 10 秒暂停间隔的 10 秒窗口会在 110 秒内产生 300 万个脉冲。

由于 EFT 测试不涉及导体的直接接触,而是通过电容钳进行间接应用,因此选择具有内部屏蔽的适当工业级布线可以通过大幅衰减 EFT 能量的耦合来对 DUT 产生巨大的补救措施进入导体。图 10 提供了 EFT/突发脉冲群抗扰度测试的图形表示,供您参考。

图 10. 根据 IEC61000-4-4 进行 EFT 抗扰度测试

浪涌抗扰度

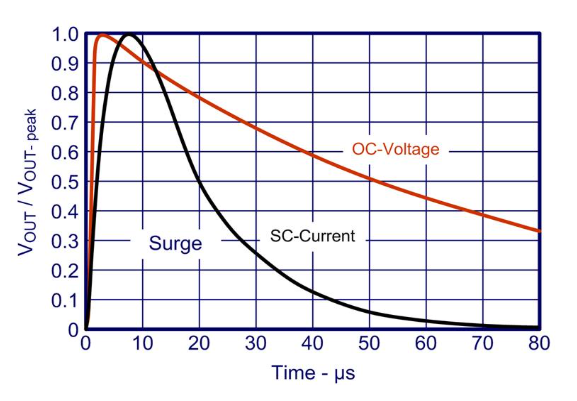

浪涌抗扰度测试 IEC61000-4-5(图 11)是电流和持续时间点上严格的瞬态抗扰度测试。然而,其应用往往仅限于长信号线和电源线(L > 30m)。浪涌抗扰度测试通常被称为“雷击测试”,因为它模拟雷击(直接雷击或间接雷击引起的感应电压和电流)引起的开关瞬态,或开关电源系统,包括负载变化和短路。

浪涌发生器的输出波形是针对开路和短路条件指定的。开路峰值电压与峰值短路电流之比就是发电机的输出阻抗。该测试的特点是由于发生器阻抗低而产生高电流,并且脉冲持续时间长(大约比 ESD 抗扰度和 EFT 抗扰度测试长 1000 倍),表明是高能量脉冲。

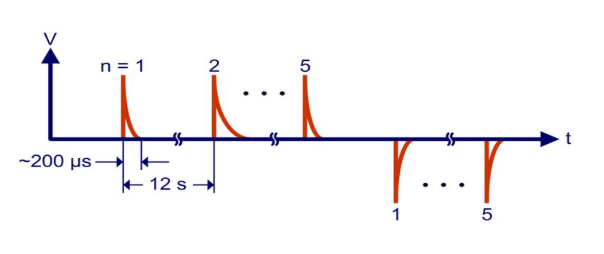

该测试需要五个正浪涌脉冲和五个负浪涌脉冲,连续脉冲之间的时间间隔为一分钟或更短。常见的程序是将暂停间隔缩短至 12 秒,从而将总测试时间减少到两分钟以下。虽然这种方法加剧了浪涌影响,但由于保护电路减少了脉冲之间的恢复时间,因此有助于显着降低测试成本。 有关浪涌抗扰度测试的图形表示,请参见图 11 。

图 11. 根据 IEC61000-4-5 进行浪涌抗扰度测试

系统级测试总结

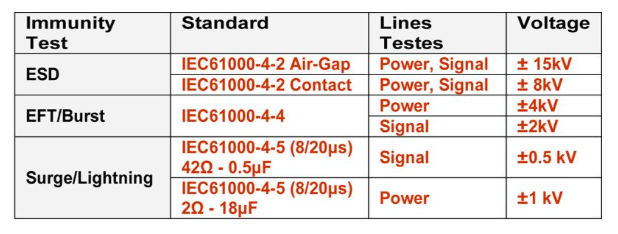

系统级测试标准由 IEC 根据 IEC61000-4 规范编制。虽然该规范系列中列出了大约 25 个系统级测试标准,但涉及瞬态抗扰度测试的标准包括:ESD (IEC61000-4-2)、EFT/突发 (IEC61000-4-4) 和浪涌/闪电 (IEC61000) -4-5)。表 2 提供了这些系统级测试的比较。

表 2:系统级测试的比较。