1 前言

电磁兼容,即EMC(Electromagnetic Compatibility),是指干扰可以在不损害信息的前提下与有用信号共存。随着数字化产品的不断问世,其电磁兼容性的设计越来越引起人们的重视。因为高速数字电路工作时,会产生大量的高频干扰信号,处理不好,不仅影响本身性能,而且还会影响周围环境。以VCD机为例,VCD机中有高速数字信号处理电路,存在大量的脉冲干扰,处理不当,将影响音视频的质量和读盘纠错能力。严重时高频干扰脉冲会通过电源或空间发射出来,影响周围电子设备的正常工作。现以VCD机为例讨论数字AV产品的抗干扰设计。

2 数字AV产品的特点

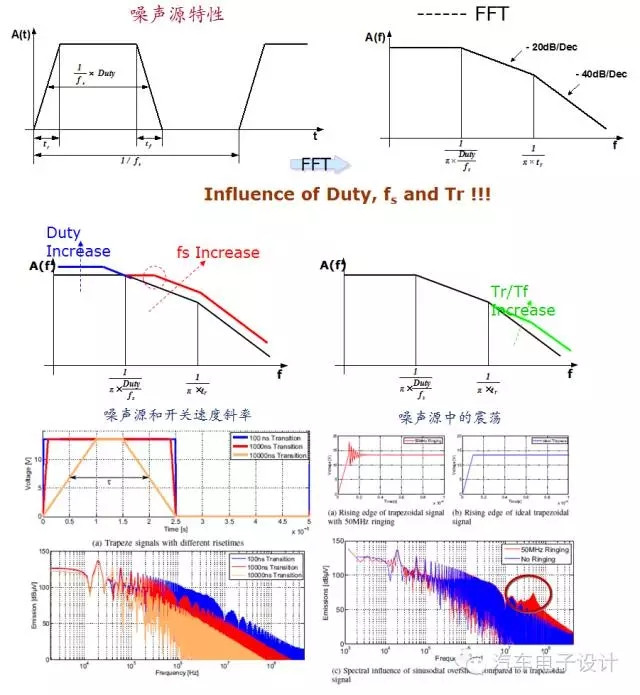

目前,数字AV产品除了廉价大众化的VCD机外,为了满足广大用户对音视频产品的品质要求,厂商又不断地开发DVD和数字电视等数字AV产品。数字AV产品的核心是DSP(Digital Signal Processor)系统,对音视频信号进行高速的数字信号处理,使人们视听享受达到较完美的境地。同时,由于数字信号处理的码率很高,如VCD视盘机MPEG1视频数据率和音频数据率之和约1.5 Mb/s;DVD MPEG2音视频可变码率平均为4.69 Mb/s,最大速率达10.7 Mb/s,可见码率之高,处理系统又与高速的存储器配合使用进行数据的读写。随着码率的不断提高,数字信号处理的速度越来越快,产生与速度成正比的大量干扰脉冲,且频率越来越高,幅度越来越大,结果对产品的抗干扰设计带来更大的难度,也是产品品质高低的关键所在。

3 数字电路的常见干扰噪声

对数字AV产品这样一个数字信号处理系统来说,常见以下几种噪声:

(1)电源噪声:在该数字系统中,主要由于受DSP电路、CPU、动态存储器件和其它数字逻辑电路在工作过程中逻辑状态高速变换造成系统电流和电压变化产生噪声,温度变化时的直流噪声以及供电电源本身产生的噪声等等。

(2)地线噪声:在系统内,如果在各部分的地线之间出现电位差或者存在接地阻抗便会引起接地噪声。

(3)反射噪声:传输线路各部分的特性阻抗不同或与负载阻抗不匹配时,所传输的信号在终端(或临界)部位发生反射,使信号波形发生畸变或产生震荡。

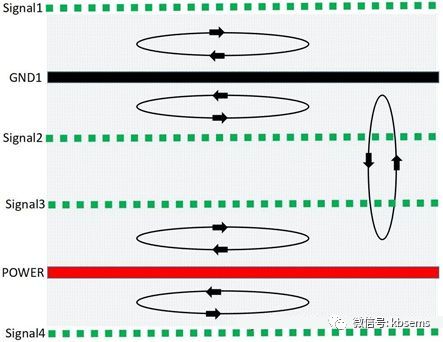

(4)串扰噪声:产生原因是由于扁平电缆或束捆导线等传输线之间,印制电路板内平行印制导线之间的电磁感应,以及高速开关电流通过分布电容等寄生参数把无用信号成分叠加在目的信号上引起的。

4 电源和地线噪声的抑制

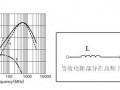

在数字AV产品中大量地应用了CMOS的数字器件和数字模拟混合器件,如DSP芯片、CPU、动态RAM、D/A变换器和其它数字逻辑器件,当设备工作时这些器件同时工作会使电路板内的电源电压和地电平波动,导致信号波形产生尖峰过冲或衰减震荡,造成数字IC电路的噪声容限下降,而引起误动作,其原因是数字IC的开关电流I和电源线、地线的电阻R所造成的电压降eR=IR与印条和元器件引脚的分布电感L所造成的感应电压降eL=L(dI/dt)两者一起作用。

由图1的模型可以进一步说明,假如线路中的电流从50 μA变成2 mA,上升沿为10HHns,则电阻引起的压降为:eR=IR=2×200=0.4,单位是mV,电感引起的压降是:eL=L(dI/dt)=400 ×(2-0.05)/10≈78,单位也是mV。

可见由分布电感引起的电压降相当大。由于数字AV产品中有好多条高频数字信号线,因此,电源和地线的干扰是相当严重的。

其次,由于一部分CMOS电路是数字模拟混合器件,如D/A转换器件,根据CMOS的基本理论,数字模拟二部分电路形成在同一个N-型的芯片上,假如只有数字部分电源VDD供电,尽管模拟电源未接,VDD的电能会转换到模拟部分N+上去,VDD电压依然会出现于模拟电源VCC脚上。同样,VDD上存在的噪声亦会出现在VCC上,由于VDD和VCC上的噪声作用造成数模混合电路,如音频D/A PCM1710的THD+N和动态范围下降,影响整机的性能。)'aH

为了抑制电源和地线噪声,在数字AV产品设计中可以采取以下措施:

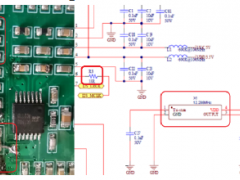

(1)选用贴片元件和尽可能缩短元件的引脚长度,以减小元件分布电感的影响;选用噪声容限大的数字IC。

(2)在VDD及VCC电源端尽可能靠近器件接入滤波电容,以缩短开关电流的流通途径,用10 μF铝电解和0.1μF独石电容并联接在电源脚上。对于MPEG板主电源输入端和MPEG解码芯片以及DRAM,SDRAM等高速数字IC的电源端可以用钽电解电容代替铝电解,因为钽电解的对地阻抗比铝电解小得多。

(3)印制板布局时,要将模拟电路区和数字电路区合理地分开,电源和地线单独引出,电源供给处汇集到一点;PCB布线时,高频数字信号线要用短线,主要信号线最好集中在PCB板中心,时钟发生电路应在板中心附近,时钟扇出应采用菊链式或并联布线,同时电源线尽可能远离高频数字信号线或用地线隔开。

(4)印制板的电源线和地线印制条尽可能宽,以减小线电阻,从而减小公共阻抗引起的干扰噪声。

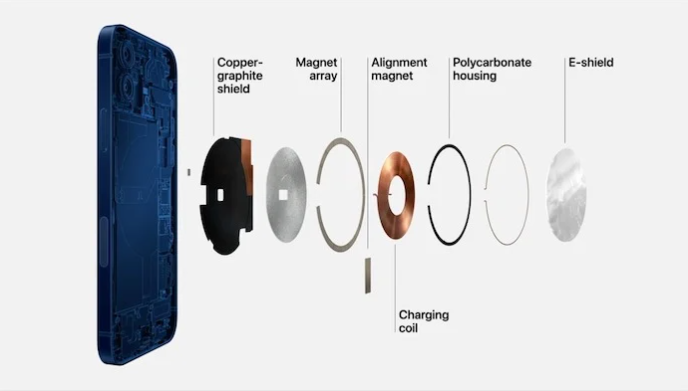

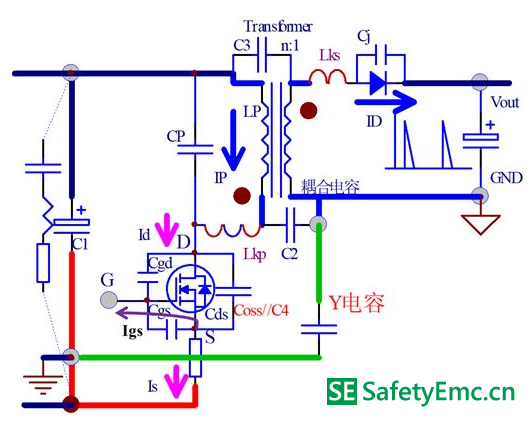

(5)对数模混合电路,VDD与VCC应该联到模拟电源VCC,AGND与DGND接到模拟地AGND,如图2所示,根据BB,PHILIPS,东芝公司实验结果,建议把D/A器件视为模拟器件,MPEG电路与D/A器件连接如图3,D/A器件必须置于AGND上,同时要提供一条数字回路供这些数字噪声/能量反馈回信号源,以减小数字器件的噪声对模拟电路的影响,使D/A器件的动态特性提高。

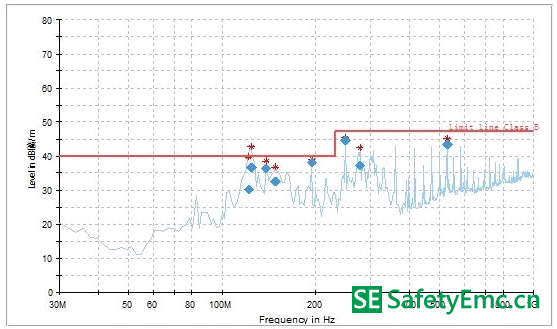

实测VCD机MPEG解压板数字电源VDD与模拟电源VCC的噪声电平如图4所示,由波形可知,电源上叠加的噪声电平已相当小,VDD噪声电平与VCC噪声电平波形基本一致,且数字电源噪声电平明显大于模拟电源的噪声电平,这说明这些干扰脉冲主要由数字信号产生的。

苏公网安备32050802011615号

苏公网安备32050802011615号