高速模拟电路中的ESD 保护电路设计

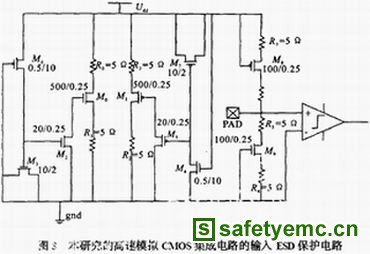

图3 是文中提出的应用于高速模拟电路的输入ESD 保护电路。 该电路的左半部为对称的两个嵌位电路,分别检测正、负ESD 电压,其中M6 , M4 等效为电阻,而源漏衬底短接的M3 , M7 等效为电容。当正的ESD 电压产生时,即某一瞬间,到Udd 有一个正的大电流, 最左边的嵌位电路工作, 大尺寸(500/ 0.25) 的NMOS 管M0 导通,泻放ESD 电流,其中R0 , R1 为MOS 管的寄生电阻。 一般来说,芯片的上电时间为毫秒级,而ESD 造成的芯片上电时间为纳秒级,因此很容易将它们区分开来。 设计时RC应该大于ESD 脉冲的时间常数(100 p F ×1. 5 kΩ)(人体模型的典型值) ,同时短于一般上电的时间常数。 这样方可保证在正常的电源上电过程中,M0 管是关闭的。

由于ESD 器件依赖电压的非线性输入电容连接到模拟电路输入管脚,往往会导致电路不能正常工作,因此,对于模拟电路的ESD 保护电路设计,除了要能满足芯片所要求的人体模型下的耐压要求,所遇到的最大的挑战是使管脚的输入电容(包括ESD 保护器件以及压焊盘上的电容之和) 尽可能小并且保持恒定。 而文中提出的ESD 保护电路在0. 25μm 的CMOS 工艺中,可以承受HBM 下的2. 5 kV 的ESD 电压, 并且输入电容只有0. 6 p F。为了减小管脚上的输入电容,M8 和M9 的尺寸不能太大,虽然ESD 电流泻放的主要器件M0 和M1 的尺寸很大,结电容也很大,但是该电容并没有连到压焊盘上,所以该电路可以承受较高的ESD 电压,同时输入电容又比较小。

该ESD 保护电路的输入电容Cin = CPAD + Cn +Cp ,其中, CPAD 为PAD 上电容,NMOS 和PMOS 上漏极电容为Cn和Cp 。 PAD 上电容相对固定,可以通过一些优化来减小。 漏极电容主要有两部分组成:漏极和栅极之间的电容、漏极的结电容。 在版图不变的情况下,漏栅电容大小基本不变,但漏极结电容会随着漏极电压的变化而出现较大变化。 当输入信号的电压幅值增大时,NMOS 的漏极结电容会变小,而PMOS 的漏极结电容却会增大。 因此,在信号电压幅值变化的时候, PMOS 和NMOS 的漏极结电容可以形成互补,总的寄生电容相对稳定。 文中提出的电路在保证合适的耐压要求前提下,输入电容较小并且能保持相对恒定,所以比较适合应用于高速模拟电路。

对于每一个输入或输出管脚来讲,按照对地或对电源放电的不同,可以分为4 种放电模式[3 ] :正电荷对地( Positive to Uss , PS) 、负电荷对地(Negative to Uss , NS) 、正电荷对电源( Positive toUdd , PD) 以及负电荷对电源( Negative to Udd ,ND) 。 因此在设计ESD 保护电路是需要考虑上述4种不同的放电模式。

以下分析该电路的基本工作原理,由于同一个MOS 管在不同的ESD 电压极性下的耐压值也大不相同,NMOS 管在NS 模式下的耐压值一般高出PS模式下10 倍以上,而PMOS 管在PD 模式下的耐压值高出ND 模式下10 倍以上,而一块芯片的耐压能力是由其所有管脚在所有模式下的最低耐压值所决定的,故要分析4 种放电模式下的电路工作原理,尤其是注意PS 和ND 模式下的放电途径。

该保护电路在NS 模式下通过M9 释放ESD 电流,在PD 模式下通过M8 释放,均能达到较高的耐压值(见表1) 。 当放电模式是PS 模式时,利用电源间的保护电路来形成一条新的放电路径,电流通过ggPMOS(M8 ) 正向偏置的寄生二极管流向Udd ,Udd和GND 之间的电压升高,M6 和M3 构成的RC 检测电路,触发大尺寸的MOS 管(M2 , M0 ) 迅速导通,在Udd 和GND 之间形成通路, 有效放电。 由于ggPMOS 的寄生二极管处于正向偏置,Udd 和GND之间泻流管尺寸很大,所以电路可以承受很大的电压。 在ND 模式下原理类似,即通过ggNMOS ( M9 )正向偏置的寄生二极管,以及中间的钳位电路泻放ESD 电流。 图4 是上述Udd到Uss片上保护电路原理的示意图。