Spice 仿真以及ESD 测试结果

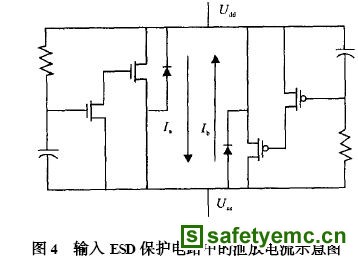

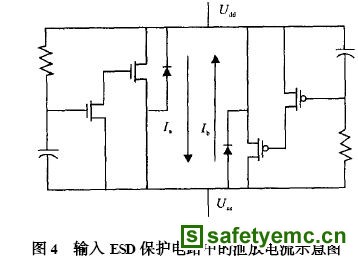

Spice 仿真以及ESD 测试结果 由于ESD 保护电路以及封装所带来的寄生电容和寄生电感对原有输出信号会有影响,尤其是在高速模拟电路中,频率越高信号畸变越严重,所以建立合适的仿真模型并进行有效的仿真是必须的。信号一般经过驱动, ESD 保护,和封装引线才能传到芯片外的负载上,封装的模型根据选用的封装形式和厂家提供的参数决定。 一般IC 封装会给出端口的寄生电容,电阻和电感,其等效模型如图5所示。 将该模型与前面的ESD 保护电路(图3) 串连起来就可以得到端口模型, 可用spice 对用于USB2.0 的环境,在480 MHz 频率下的收发电路进行仿真,其仿真波形如图6 所示。 输出端口out1 是不考虑端口模型的影响,480 MHz 时钟的输出较为理想,out2 是加入端口模型后的时钟输出,波形有所畸变,但仍能满足电路设计要求。

上述ESD 保护电路(见图3) 在被应用于设计USB2. 0 接口芯片中。 该芯片的最高时钟频率为480 MHz ,采用TSMC 公司的0. 25μm 混合信号工艺进行了流片。 流片后的芯片用抗静电测试仪( Thermo Keytek 公司,型号: ZAPMASTER 714)进行了测试,其结果如表1 所示,给出了在上述4 种不同的放电模式下的耐压值。 测试结果表明在所有测试条件下的人体模型最高击穿电压(V) 超过了正负2 500 V。

结 论

在高速的模拟电路设计中, ESD 成为芯片能否正常工作的重要考虑因素。 文中提出了在用栅极接地的NMOS 和栅极接电源PMOS 管的基础上,结合电源与地之间的高速静电泻放回路的新的电路结构。 经过实际测试,在HBM 模型下可以承受正负2 500 V 的高压,并且该电路对正常信号的影响。

ESD保护二极管选型详解

ESD(静电放电)保护二极管的选型核心在于 “因势利导” :为正常信号提供“无阻力”通路,为异常ESD脉冲提供“低阻力”的泄放通路。选型过程就是围绕这一核心,匹配电路需求与二极管参数的过程。一、明确被保护对象

0评论2025-09-23108

静电放电测试标准讲解及解析

在现代电子设备的设计与生产中,静电放电(Electrostatic Discharge,ESD)是一个不容忽视的重要问题。静电放电不仅能够直接损坏敏感的电子元件,导致系统故障,还可能因静电累积导致性能不稳定、数据丢失等严重后果

1评论2025-06-07564

静电放电测试标准——理解和比较差异

人体模型 (HBM) 器件级测试是 ESD 测试常用的模型。它用于表征电子元件对 ESD 损坏的敏感性。该测试模拟人体对电子元件的放电,如果人体积累了残余电荷(例如,穿着袜子拖着脚走过地毯)并触摸电子设备,就会发生这

0评论2025-03-23319

电路级静电防护设计技巧与ESD防护方法

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用

3评论2021-01-28800

电路保护的意义是什么?常用的器件有哪些?

电子电路很容易在过压、过流、浪涌等情况发生的时候损坏,随着技术的发展,电子电路的产品日益多样化和复杂化,而电路保护则变得尤为重要。电路保护元件也从简单的玻璃管保险丝,变得种类更多,防护性能更优越。电路

1评论2020-10-19270

手机开发过程中 预防ESD失效的方法

现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁骚扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、电路及接口电路造成的破坏等问题越来越引起人们的重视。目前手机的功能越

0评论2018-12-25425

解析PCB板设计中抗ESD的常见防范措施

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件

2评论2018-12-25567

如何提高隔离接口模块的ESD抗扰能力?

隔离模块应用于各类复杂的工业环境中,以提升总线的抗干扰能力,但设备接口可能会采用端子与外部连接,可能会在安装、维修过程中有静电等能量输入,从而导致隔离模块损坏。那么该如何避免这样的问题呢?本文为您揭秘

0评论2018-07-02866