2 . 产品详细方案设计

2.1 产品原理图设计规范及检查列表

在产品原理图设计阶段主要对产品内部的硬件设计细节,主要是电源/主芯片/强辐射信号/敏感信号/接口电路/ESD电路/接地等预先考虑应对措施,是保证产品良好EMC性能的基础步骤,要给予足够的重视。

EMC工程师依据检查列表进行把关检查。

2.1.1原理图设计规范

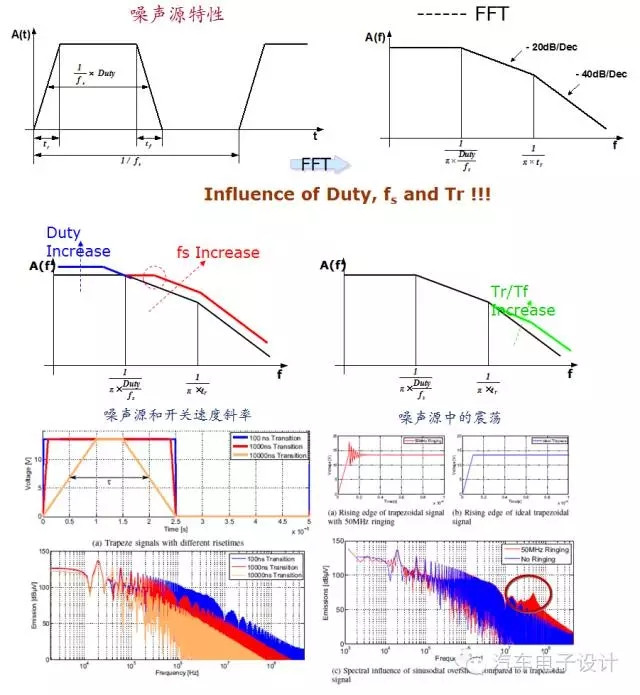

2.1.1.1数字信号回路(包括时钟电路)的阻抗匹配和谐波控制

在满足电路对信号要求的情况下,使信号边沿尽可能缓,以降低谐波分量电平。一般做法是在信号输出端串联一个电阻R,此电阻与分布电容来对信号边沿进行控制;

同时,此电阻也可以用来进行阻抗匹配,一般器件的输出阻抗为十几个欧姆,而PCB板上的走线阻抗Z0范围为50~90欧姆,导致非常严重的失配,一般采用串联一个电阻的方式进行匹配,电阻的选择可以在10~51欧姆之间,并靠源端尽可能地近。对于辐射严重的场合, 可以尝试用磁珠代替电阻来进行谐波抑制。

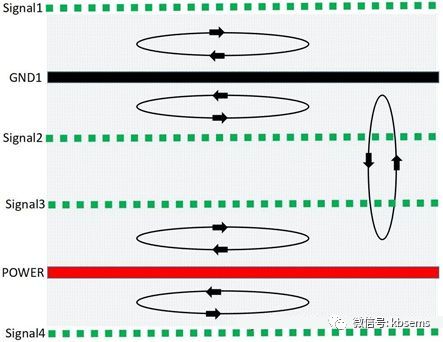

2.1.1.2差分信号的EMI辐射抑制

对于差分信号,如DDR的时钟、LVDS信号等,除了串联电阻进行阻抗匹配抑制差模辐射外,EMI主要表现为共模方式,所以此时可以在电路中串入共模抑制电感来降低辐射,采用共模电感会改变信号的相位。如下图:

2.1.1.3 PCB

板上引出线对地加适当的滤波电容,防止干扰信号从引出线辐射产品的电磁辐射源除了通过器件和PCB走线直接向外辐射外,还通过PCB上的引出线向外辐射,每一根引出线都是一个小型天线,因此在每一根引出线上对地加适当的滤波电容,对于抑制辐射有很大的作用,如果在电容前串联适当的磁珠会有更好的效果。

但要注意电容的容量要以不影响电路正常工作的信号为限。

2.1.1.4芯片的去藕滤波措施

数字芯片在工作时产生的高频开关噪声将沿电源线传播、辐射。滤波电容的主要功能就是提供一个低阻抗高频通路,将开关噪声以最短的路径短路到地。由于这是一个高频电流环路,会产生EMI辐射,因此滤波电容应尽可能靠近芯片的引脚,以减少环路面积,降低辐射。一般做法是每个电源引脚加一个100nF的电容。这些做法对于时钟等芯片尤其重要。

由于电容非理想器件,不同容量的电容对一定频段信号的滤波效果不同,在电容的谐振频率附近可得到最好的滤波效果,如下表所示。对于工作频率很高的器件,应采取多个不同容量电容并联使用。这样可以在很宽的频率范围内得到比较好的滤波效果,降低电源网络的高频开关噪声。

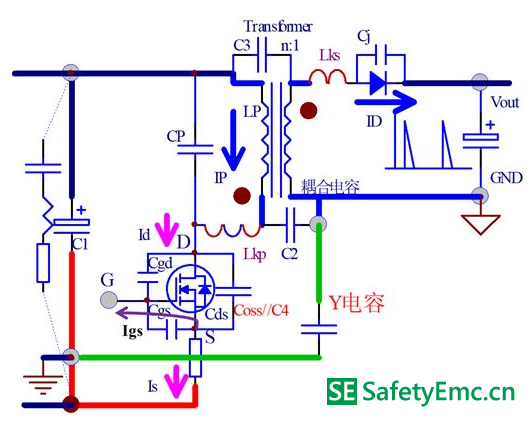

2.1.1.5三端稳压器或开关式

DC/DC电压变换电路输入/输出端的滤波措施对于三端稳压器,尤其是LDO,输入/输出端必须有一定容量的去耦电容,否则电路可能工作不稳定,甚至产生自激振荡,建议用10uF以上电解电容加小容量的陶瓷电容并联使用,电流越大,容量越大。

对于DC/DC电压变换电路,由于其工作频率较高,脉冲电流大,要使用高频特性好的滤波电容,最好是大容量的陶瓷电容与电解电容并联使用,由于不同厂家型号器件特性不同,可以参考其规格书来选用滤波器件参数。为了防止开关脉冲电流串入系统其它部分引起干扰,此部分电路的输入端要用磁珠或电感与其它电路隔离。

2.1.1.6信号输入端的ESD防护措施

整机对外的信号接口必须具有防静电的保护措施,可以使用的器件有:

瞬态电压抑制器(TVS)、压敏电阻(MLV)、二极管(稳压二极管、肖特基二极管)、电容等。由于不同信号的频谱范围不同,对ESD器件的电容量有不同的限制,此外还需要考虑成本、寿命等其它特性,综合均衡来选取最合适的器件。其中TVS有更低的箝制电压、更低的漏电以及更快的响应速度,价格也最高。

2.1.1.7 FLASH和EEROM的写保护,防ESD冲击丢失数据

对于整机中储存程序和数据的FLASH和EEROM,由于工作时经常需要对其进行读写操作,当受到静电的冲击时,容易造成数据丢失。 将其写保护引脚用MCU控制,可以有效地保护芯片。

2.1.1.8 MCU及主芯片GPIO口的防干扰措施

在引脚上串联适当大小的电阻可以保护IO口免受冲击,在输入脚对地并接适当容量滤波电容,可以过滤干扰信号,防止误动作。

2.1.1.9复位信号的滤波处理

因为复位信号在pcb上一般走线比较长,当出现静电冲击时,很容易受到干扰。因此应尽量保持复位信号线路的低阻抗,并在器件复位脚附近增加对地滤波电容。

2.1.2 原理图设计EMC检查列表