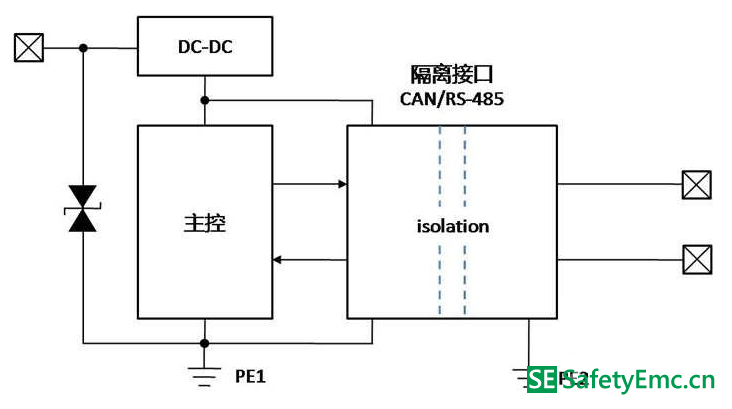

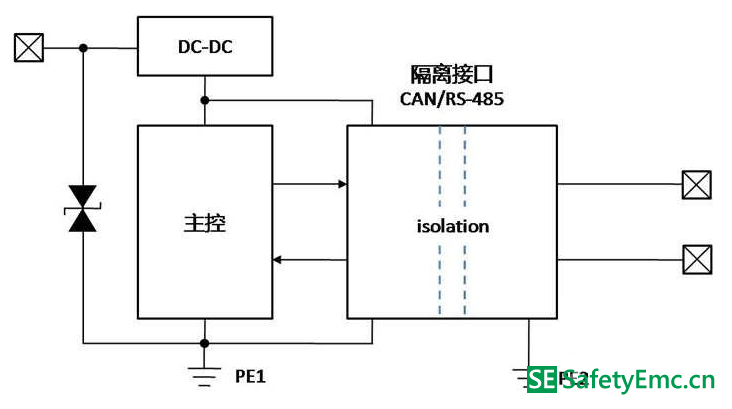

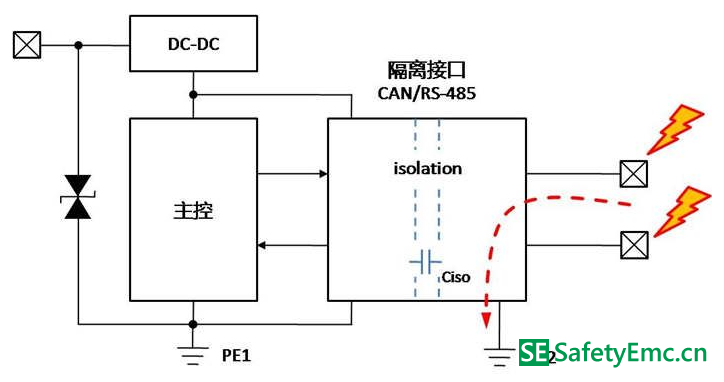

3. 设备控制侧、总线侧均有接保护地

如图 10,此状态下,设备控制侧、总线侧都通过一定方式接入保护地(PE)。

图 10

状态出现的可能场景:

1. 设备自身接PE,总线组网后单点接PE。

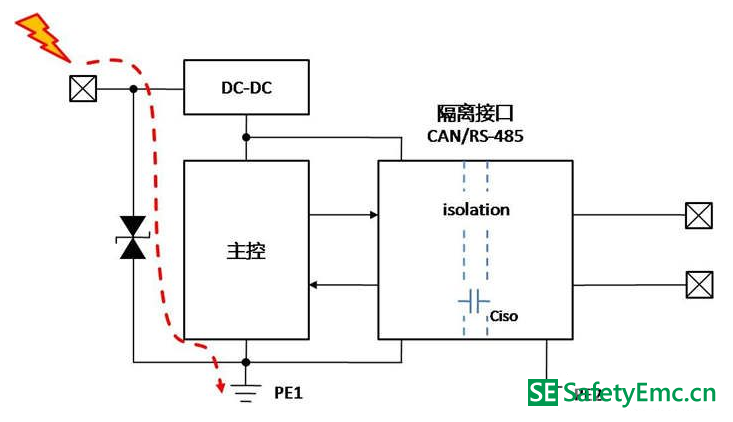

静电分析:

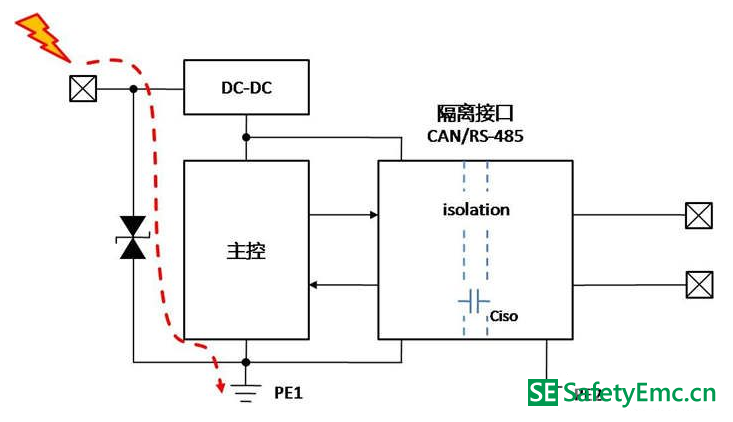

当控制侧接口受到静电放电时,能量通过控制侧保护器泄放至PE1,对隔离通信接口基本无影响,如图 11。

图 11

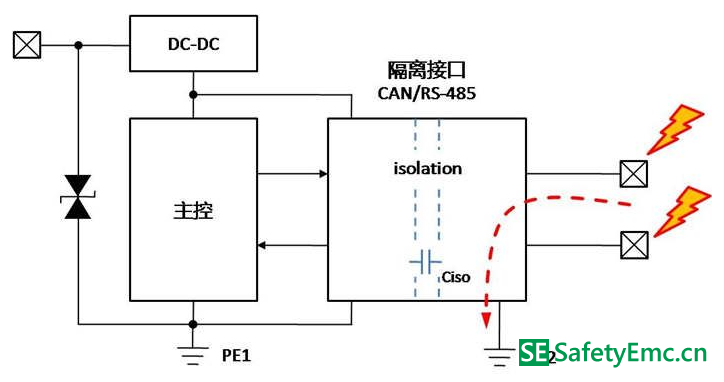

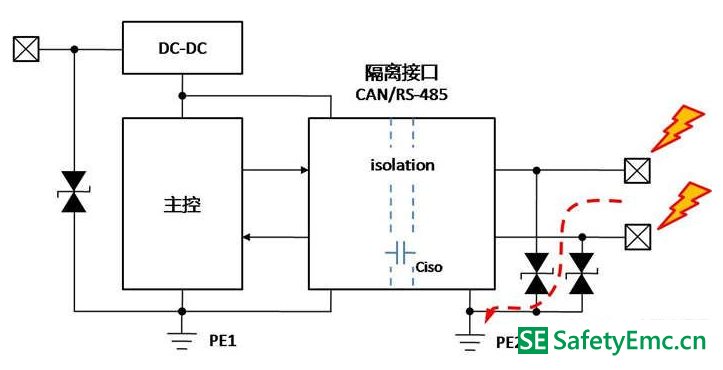

当总线侧接口受到静电放电时,静电能量通过隔离接口模块内部总线侧器件泄放至PE2,如图 12。若ESD能量超出了接口模块内部总线侧器件的ESD抗扰能力,总线接口则可能损坏。

图 12

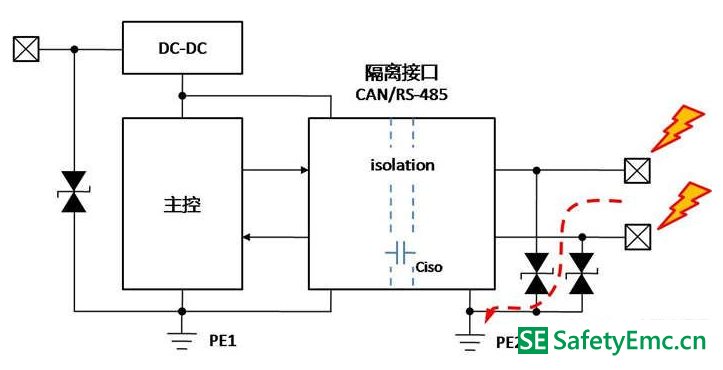

改善方法:

在总线侧增加高等级ESD防护器件(如TVS管),静电能量会通过防护器件泄放至PE2,由此来提高总线侧的静电能力,如图 13。

图 13

推荐的实际应用电路:

为了满足上述提到的三种设备状态下,隔离接口模块均得到有效的静电保护,建议进行隔离接口设计时,参考图 14所示电路,增加Cp、Rp以及TVS,提高隔离接口的ESD抗扰能力。注意,若产品有安规要求,如需要进行耐压测试、绝缘电阻测试,则不能增加Rp电阻。

图 14

总结:

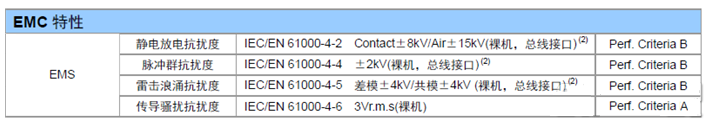

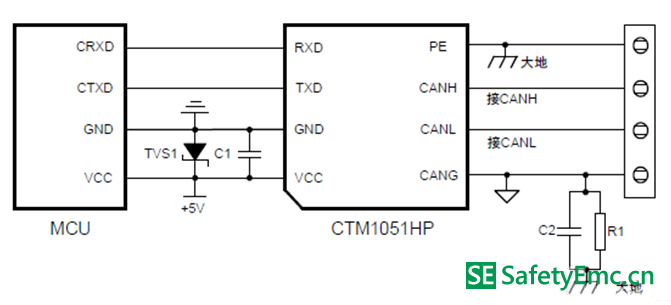

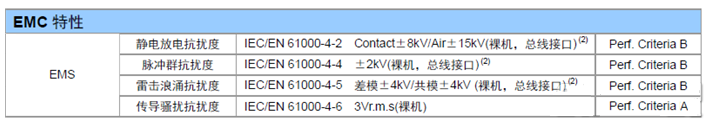

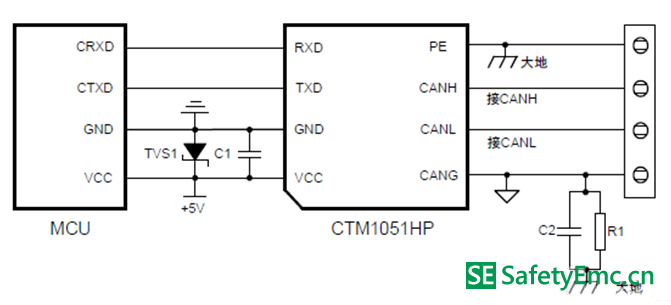

由于设备实际应用中会存在各种不同的状态,对于与上述描述不同的情况,也可按以上的方法进行分析,并有针对性的增加保护器件,从而达到提升ESD抗扰能力的作用。广州致远电子有限公司基于多年的总线防护设计积累推出了高防护等级隔离模块——CTM1051(A)HP系列。该系列符合国际ISO11898-2标准,静电防护等级可达接触±8kV,空气放电±15kV,浪涌防护可达±4kV隔离CAN解决方案,具体如下图15所示,能够适用于各种恶劣的工业现场环境。应用简便,即插即用,应用原理图如下图16所示。

图15 CTM1051(A)HP的EMC性能

图16 应用原理图

ESD保护二极管选型详解

ESD(静电放电)保护二极管的选型核心在于 “因势利导” :为正常信号提供“无阻力”通路,为异常ESD脉冲提供“低阻力”的泄放通路。选型过程就是围绕这一核心,匹配电路需求与二极管参数的过程。一、明确被保护对象

0评论2025-09-23146

静电放电测试标准讲解及解析

在现代电子设备的设计与生产中,静电放电(Electrostatic Discharge,ESD)是一个不容忽视的重要问题。静电放电不仅能够直接损坏敏感的电子元件,导致系统故障,还可能因静电累积导致性能不稳定、数据丢失等严重后果

1评论2025-06-07599

静电放电测试标准——理解和比较差异

人体模型 (HBM) 器件级测试是 ESD 测试常用的模型。它用于表征电子元件对 ESD 损坏的敏感性。该测试模拟人体对电子元件的放电,如果人体积累了残余电荷(例如,穿着袜子拖着脚走过地毯)并触摸电子设备,就会发生这

0评论2025-03-23337

电路级静电防护设计技巧与ESD防护方法

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用

3评论2021-01-28822

电路保护的意义是什么?常用的器件有哪些?

电子电路很容易在过压、过流、浪涌等情况发生的时候损坏,随着技术的发展,电子电路的产品日益多样化和复杂化,而电路保护则变得尤为重要。电路保护元件也从简单的玻璃管保险丝,变得种类更多,防护性能更优越。电路

1评论2020-10-19280

手机开发过程中 预防ESD失效的方法

现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁骚扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、电路及接口电路造成的破坏等问题越来越引起人们的重视。目前手机的功能越

0评论2018-12-25432

解析PCB板设计中抗ESD的常见防范措施

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结;短路正向偏置的PN结;熔化有源器件

2评论2018-12-25580