换言之为了使Decoupling Condenser可作高速动作,因此需设法使电感成份降至最低水准,常用手法是选择chip ceramic condenser作对策,该组件通常是设于电源‧接地端之间导线长度最短的区域,藉此降低电感成份。在IC/LSI众多组件种类之中,有些组件有考虑电源‧接地端的layout与Decoupling Condenser组装问题,有些组件则未考虑上述问题。多层电路板的电源‧接地是由batter面构成,因此电源‧接地即使是高频性,仍可见到阻抗(impendence)成份。IC/LSI用Decoupling Condenser的电荷属于低阻抗,所以祇要补正IC/LSI不足的驱动电流,高频电流就可以通过电源层流动。具体对策如图4所示,在电路上装设高频用inductor,如此一来就可提高高频阻抗(impendence),进而防止switching时的动作电流流出电源侧。如上所述当switching时,高频贯穿电流会在CMOS LSI内部电源与接地之间流动,为了抑制IC/LSI的高频大电流集中在电源‧接地之间流动,同时减轻单位pin的电流,因此将电源与接地端子作多脚化(multi pin)设计成为常用的手段。如图5所示实际pattern封装设计时,并非概括性的设置Decoupling Condenser,而是在每个电源‧接地之间设置Decoupling Condenser。

(d).信号线的终端

要让数字号产生的高频波频宽降至最低范围,基本上必需防止传输线路不整合所造成的over shoot与linking波形变动,因为如此一来除了可以防止电路误动作之外,还可使放射噪讯频宽变窄。图6是常用的对策方式,这种对策也称为终端法,不过最有效的终端法是并列终端法与Tabnan终端法。

(e)降低电流loop面积

某点的电磁波电界强度 可用下式求得:

E=K(f2AI/r) ------------------------(2)

K:定数

f:频率

A:电流loop的面积

I:电流loop的电流大小

r:至电流loop的距离

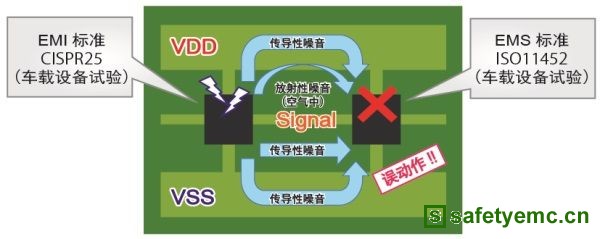

由式(2)可知降低电界强度的条件是抑制 ,增加 值,也就是说要降低放射能量必需增加loop电流值,减少loop面积与频率同时加大物理距离。loop面积最小化意味着可以降低从该处放射的噪讯能量,同时还可以避免成为噪讯放射至外部的天线,使得电子机器不会产生或是接受噪讯,进而获得EMC防护对策的预期效果。除此之外layout封装线路时,必需注意平行邻接且长度较长的pattern,很容易发生cross talk使得噪讯值无法降低,因此必需特别谨慎处理。

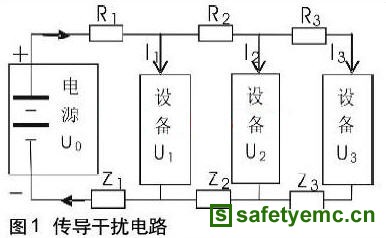

电路基板封装时的电气性

文接着要探讨有关layout封装线路时的噪讯对策。基本上信号系导线即使完全按照电路图的设计,同时将各电子组件用导线连接,祇要适度控制pattern的长度,理论上低频领域的信号还不致发生动作特性上的困扰。不过由于pattern导线本身就具有电感(inductance)成份,因此随着动作频率的增高,电感的影响逐渐表面化,同时开始对信号线与电源系统造成预期外的障碍,因此layout封装线路时必需注意下列事项:

①连接各电子组件的信号线电源‧接地导线pattern,必需全部与inductance连接,尤其是使用双面印刷电路板的场合,更需作精密通盘的检讨。

②已经装有电子组件的印刷电路板,基本上就会有所谓的浮游容量,尤其是inducta nce的power line上,会布满整面浮游容量的「powder」。浮游容量的影响随着频率的增加,使得浮游容量变成无法忽视的潜在性问题。

③平行邻接的两条pattern导线,具有静电容量与电感(inductance)成份。

接下来要介绍有关上述②、③项因静电诱导与电磁诱导造成意外性的噪讯诱导事项;上述第①项则在后段「导体的inductance」章节中有详细的说明。

(1)静电诱导

图7是静电诱导造成诱导电压的等价电路,诱导电压可利用下式求得:

V2=V1x{Z/(Z+ZS)}------------------(3)

ZS:诱导体之间的浮游容量

Z:grand与被诱导line之间的阻抗(impedance)。

由于高频电路的ZS、Z 绝对具有LC成份,因此可将高频电路当作复素数考虑。

【计算实例3】

配电管内(duct)的电线与信号线相互紧密设置,假设两者之间的结合容量为40pF/m,试算100V,50Hz的电线与信号线长度10公尺时,被信号线诱导的电压V2 。信号线ground的阻抗(impedance)为1MΩ。与10公尺长的信号线结合容量为400Pf时,电抗(reactance)ZS 计算如下:

从以上计算结果可知诱导电压由于结合容量降低获得舒缓,也就是说电力线与信号信如果能取得充分的物理间隔就是最好的对策。

2)电磁诱导

被电磁诱导的电压 可利用下式求得:

同相位电流在并行两条pattern导线内流动时,会因磁气结合变成相互电感诱导,此时的诱导电压 会与pattern直列重迭,形成被诱导pattern进而变成cross loop电流。PDX安规与电磁兼容网

【计算实例4】

pattern导线上的两条信号线,间隔 ,pattern长度 ,试算此时的相互电感(inductance) ;此外信号源的频率为100MHz,电流 时,试算此时的诱导电压 。

导体的电感

假设印刷电路板上形成的导体pattern自我电感(inductance)为 ,pattern宽度+铜箔厚度为parameter,电感与pattern长度的关系如图8所示。自我电感 的计算式如下所示:

【计算实例5】

假设独立的印刷pattern宽度w 为0.2mm,导体厚度t 为18μm,长度λ 为100mm。试算pattern的自我电感L 与导体R阻抗 。此外试算频率分别是1MHz、10MHz、 100MHz,导体的诱电率σ=0.58x108(S/m) 时的电抗(reactance)XL。

将以上数据代入式(4)与式(5),分别计算自我电感 与导体阻抗 ,其结果如下:

L= 0.146μH

R=0.47Ω

接着计算频率为1MHz、10MHz、100MHz时的电抗(reactance) ,其结果如下:

f=1MHz时 f=10MHz时 f=100MHz时

XL=0.92Ω XL=9.2Ω XL= 92Ω

由以上计算结果可知动作频率变高,在1MHz左右时阻抗(Z=R+jL∞)很低,因此pattern导线的电抗(reactance)强度还不致对电路造成影响。不过当频率变成10 0MHz时,自我电感的电抗(reactance)XL 是导体阻抗 的200倍,也就是说一旦变成100MHz时,导线pattern产生的电压下降成为无法忽视的问题,它与上述连接组件的pattern导线,在高频领域时必需考虑的电感(inductance)具有相同意义。电感(inductance) 与导体的长度与宽度具有依存特性,导体的宽度越大长度越短,越能抑制阻抗(impedance)。由图8可知自我电感具有长度方向依存特性,对宽度方向的依存性较低,例如宽度增加十倍,电感(inductance)大约降低一半左右,不过如果长度变成1/2时,电感值可改善至1/2.2以下。由此可知pattern变短是降低阻抗(impedance)非常有效的方法。电感两端发生的电压下降程度,与电流的时间变化成一定比例,电压下降e可利用下式求得:

e=L×(di/dt)----------------------------(8)

减缓电压下降可利用式(6)抑制急遽的电流变化,并降低自我电感(inductance) 。di/dt与IC的站立时间特性有关,因此限制使用超过设计需求的高速IC,成为抑制噪讯值最佳手段。不过最近的高速IC输出阻抗(impedance)一般祇有10Ω左右,站立时间为0.5n s,因此di/dt大约为 左右。

【计算实例6】

印刷电路板的条件与计算实例5相同,试算108 (A/S)电流变化时的电压e。

e=L×(di/dt)

=0.146(μH)× (A/S)

=14.6(V)

由计算结果得知由于有导体阻抗,因此产生的电压反而变低,而诱导电压的大小则超过预期。

苏公网安备32050802011615号

苏公网安备32050802011615号