整合型相位噪声之测量与相位抖动之计算

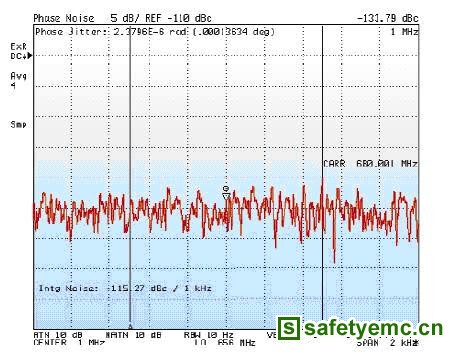

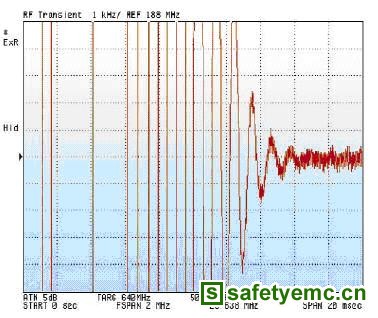

在特定的频率范围内,VCO/PLL讯号测试系统能在相同的屏幕上,显示出相位噪声和整合型相位噪声之功率,以做为改进开发和提升设计效率的参考。图十是一个测量整合型相位噪声的实例。相位噪声功率之总和〔dBc〕,在光标指定的偏移频率范围内(1kHz)之测量结果,显示在屏幕的左下角。

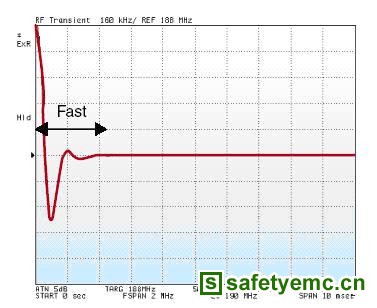

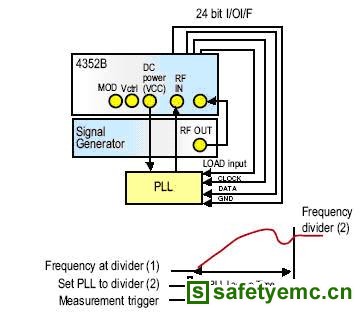

图六:射频频率和DC控制电压的量测

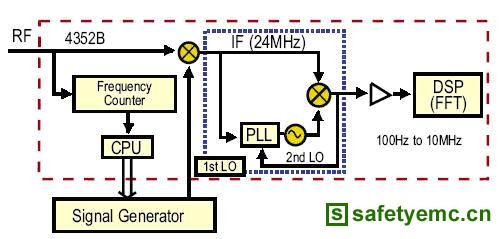

图七:载波 锁定多模块PLL电路

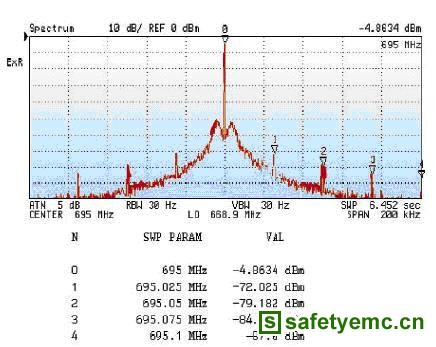

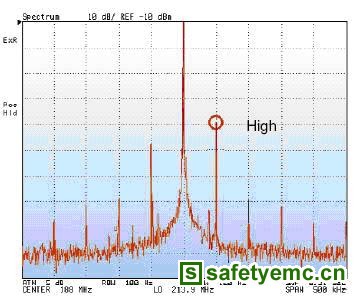

图八:VCO相位噪声的测量实例

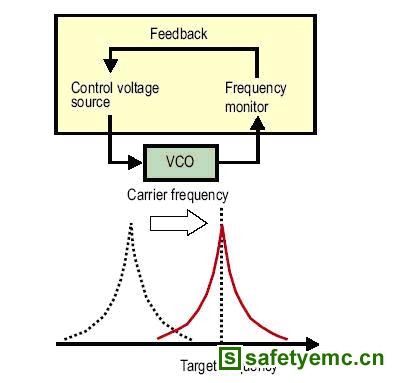

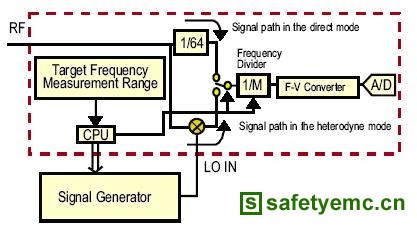

图九:自动化频率控制

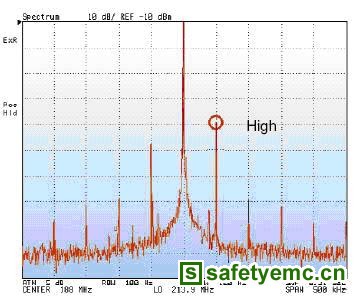

图十:整合型相位噪声功率之测量实例

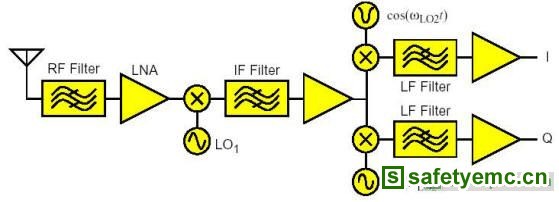

锁相回路的特性参数

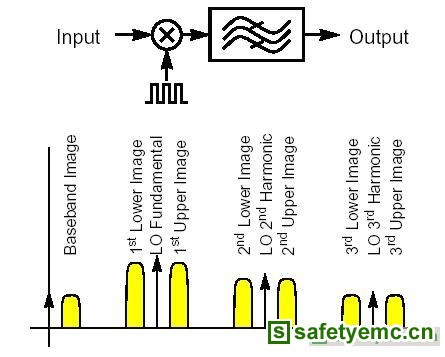

锁定时间和PLL频率合成器的寄生响应(spurious response),彼此是互为取舍(trade-off)的关系。一个PLL频率合成器一般是由许多组件构成的,因此必须考虑到每一个组件参数的可能变化量,以确保制程的质量。当设计一个优化的回路滤波器时,在PLL的原型设计时间,下列参数必须纳入评估:

1) 频率〔Hz〕

2) 射频功率〔dBm〕

3) 相位噪声〔dBc/Hz〕

4) 参考源漏泄(寄生频率特性)〔dBc〕

5) 锁定时间〔sec〕

6) 回路带宽

对PLL频率合成器做性能评估,通常需要各种不同的测量仪器,包括如下:

1) 用来测量锁定时间的调变域分析仪

2) 相位噪声测量系统

3) 评估寄生频率特性的频谱分析仪

4) PLL控制器

每次连接结束之后,必须对测量系统做性能校验,这对重复测量是必需的。当回路滤波器的特性或振荡频率改变时,测量用的组态设定也必须重新改变,而这种冗长的工作会延长产品的开发时间。因为PLL频率合成器是被设定在期望的频率上,当利用数字方式控制PLL芯片时,则一个PLL控制电路或一个PLL控制程序是不可或缺的。因此,除非直到控制电路或控制程序完全启动,否则不可能执行频率合成器的测量。因为当PLL频率一变动时,测量系统很难和它同步,PLL锁定时间就很难被精准地测得。

时间和频率的分辨率

锁相回路的特性评估

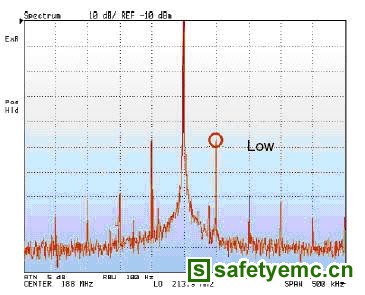

图十一:PLL寄生频率的测量实例

利用程控PLL

频率的瞬间测量

图十二:PLL芯片控制和锁定时间之测量

图十三:瞬间频率的测量方法

图十四:瞬间频率的测量实例

图十五:在较低的截止频率下之寄生特性

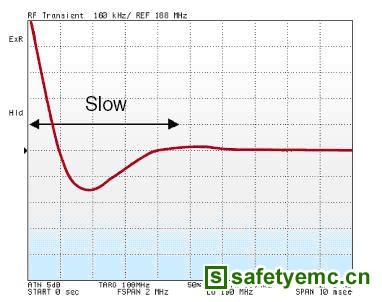

图十六:在较低的截止频率下之锁定时间特性

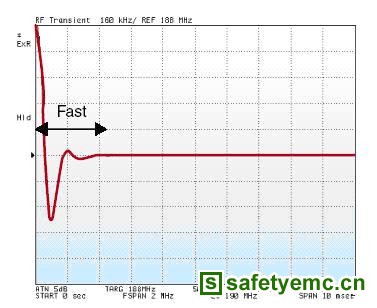

图十七:在较高的截止频率下之锁定时间特性

虽然,参考频率或回馈频率的除频器都可使用上述的数据格式来决定除频比率,但是两者的处理方法是不同的。参考频率的除频器将16位的数据,当成一个区块来处理,除数的大小范围是从5到65,535。回馈频率的除频器将16位的数据,区分成两个区块来处理,分别是20~25和26~215。此除频器里的「回收计数器(swallow counter)」处理20~25,「可编程计数器(programmable counter)」则处理26-215。两种计数器的大小范围,前者是0~63,后者是5~1023,所以此除频器的除数大小范围是320~ 65535,如下所示:

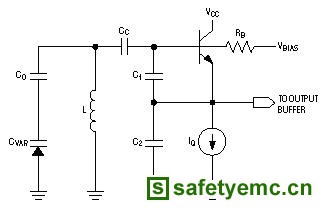

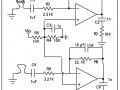

VCO电路的设计

如图十九所示,它是使用Colpitts LC振荡电路。虽然目前有许多振荡器电路可以被用来设计射频VCO,但是其中最有效益的就是Colpitts的共集级(common-collector)电路。此电路适用的频率范围很广,可以从射频到中频,它是由低价位的电感和变容二极管(varactor diode)组成,如图十九所示。这是一个并联谐振电路,电感或电容上的任何变动都会改变振荡频率。在并联模式下,允许我们能够直接对振荡器做分析。就电路特性而言,它是一种具有正回馈功能的LC放大器。在图十九中,若忽略寄生因素,CC>>C1和C2,C1>Cπ(Cπ是基级-射级之间的电容),经计算可以求得振荡频率f0为:

CO 是变容二极管的耦合电容值,CVAR是变容二极管的电容值,CT是总电容值。

集级电压是分配给C1和C2,并在射级接地。当施予负电压时,CVAR会变小,所以可以藉此调整振荡频率的大小。如果再详细研究和计算,甚至可以求得回路增益、振荡振幅、相位杂音,正如前面介绍的VCO/PLL讯号测试系统的部份功能。

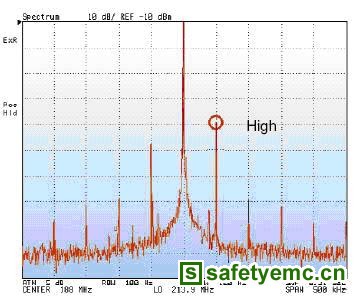

图十八:在较高的截止频率下之寄生特性

图十九:VCO的设计实例

结语

其实,射频或微波电路设计已经有百年的历史了。如今因为集成电路制程的进步和无线应用的开放与流行,突显了射频电路的重要性。设计射频电路首重基本观念、专有名词、技术规格的充分了解,唯有不断的学习、研究和实作,经年累月之后,才会有启发和成果,这是无法投机取巧的。本文所介绍的VCO/PLL测量和设计技术,包含许多设计原理和实作细节,在进行射频电路开发时,必须充份考虑,才能事半功倍。

苏公网安备32050802011615号

苏公网安备32050802011615号