在这种设计中,主PCB上的体去耦电容被放置在靠近集成电路的地方,在那里印制线的密度非常高。移动体去耦电容离开这个区域并不会减小低频去耦,而且还会为PCB上布关键性的信号印制线提供空间。图3所显示的就是体去耦电容是如何被放置在高密度的印制线区域内的。

图3 高印制线密度内放置的体电容

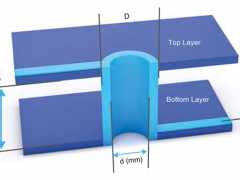

局部去耦电容的连接同样需要改进。在PCB上局部去耦电容需要放置在距离集成电路很近的地方,其间的距离大约是30密耳。另外,为了更好的效果,局部去耦电容和电源总线之间的互感需要最小化。对于大部分情况,在主PCB上局部去耦电容会被放置在靠近集成电路之处。然而,许多局部去耦电容与电源总线的连接很差。在很多时候,经过一个共用的印制线使多个去耦电容与电源面和接地面连接起来。对于接地和电源来说,这些共用的印制线上的所有电容只有一个通孔。通过这种方式连接局部去耦电容就产生了许多的互感。图4所示的就是一些被放置在PCB上的局部去耦电容。连接局部去耦电容更好的方式就是应该为每个电容在连接处提供两个通孔:一个通孔直接连接地平面,另一个直接连接电源平面。另外,去耦电容和集成电路不应该共用电源通孔和接地通孔,如果这样的话就为去耦电容提供了一条线路。为了取得最大互感的地方。为了得到最大互感,较长的电源和接地通孔应该互相紧密放置。这样,去耦电容和集成电路都被放到了PCB的最上层,并且从上到下的层叠的顺序是信号面——接地面——电源面——信号面。来自最上层的最长的通孔应该是电容和集成电路的电源通孔。因此,去耦电容和集成电路的电源通孔应该尽可能的互相靠近。如果电容被放置PCB的反面(如图5所示),那么集成电路的电源通孔和电容的接地通孔应该被放置得尽可能靠近。

图4 与电源和接地并联共用相同印制线和通孔的三个电容

图5 去耦电容的接地通孔和集成电路的电源通孔间的互电容

面间电容可以通过电源层和接地层间共同的表面积的增加而增大。在这个设计中,一些接地的临时线被布到了电源层。通过移动这些接地的临时线,并用电源层存在的电源隔离区域代替这些临时线,就会增加层间电容。

2.2 印制线布线

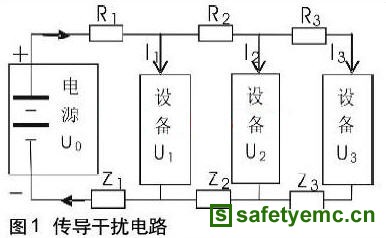

设计者通常在PCB的接地层留下间隙。这些间隙可能是接地层的高速时钟线或者其他印制线布线的结果。有时间隙置于接地层,以使板上的低频区域与高频电路隔开。由于连接器插头空隙区可能会不经意的产生间隙。当回流电流被迫绕着接地层的间隙流动的时候,间隙周围就产生了不同的电位。这个电位差可能就是EMI的原因。

在主PCB上,有一些信号层的印制线穿过了邻近接地层间隙的地方。例如,信号层上的高速数据和地址线穿过了接地层上的由时钟印制线产生的位于接地层的间隙,如图6所示。

苏公网安备32050802011615号

苏公网安备32050802011615号