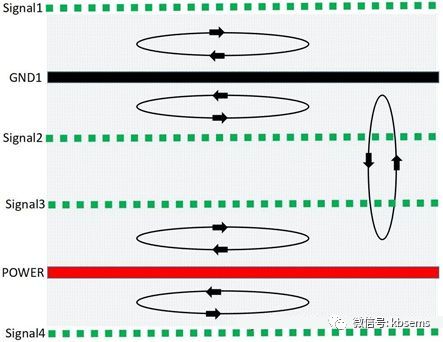

(3)接地技术

电子设备一般有两种接地。一种是安全接地,将设备机壳接地,以保护工作人员的安全; 另一种是工作接地,给电路系统提供一个基准电位,同时也可将高频干扰引走。

不正确的工作接地反而会增加干扰,如共地阻抗干扰、地环路干扰等;对共地阻抗产生的电磁干扰,可以用降低共地阻抗的方法,以减少共地阻抗产生的共阻抗耦合。

工作接地按设备工作频率采用不同的接地方式。工作频率低(小于1MHz)的设备采用单点接地式, 即把整个电路系统中的一个结构点看作接地参考点,所有对地连接都接到这一点上,并设置一个安全接地螺栓;多个电路的单点接地式又分为串联和并联两种,由于串联接地产生共地阻抗耦合, 所以低频电路最好采用并联的单点接地形式。为防止工频和其它杂散电流在信号地线上产生干扰,信号地线应与功率地线和机壳地线相绝缘。

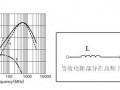

图4 串、并联地阻抗耦合

图4(串)中所示串联地阻抗耦合时,U1=I1*Z1+(I1+I2)*Z2+(I1+I2)*Z3; U2=(I1+I2)*Z2+(I1+I2+I3)*Z3; U3=+(I1+I2+I3)*Z3; U1≠U2≠U3≠Us-gnd信号地,产生串联地阻抗耦合;图4 (并)中所示并联地阻抗耦合时U1=U2=U3=Us-gnd。

工作频率高(大于30MHz) 的设备采用多点接地式,即在该电路系统里,用一块接地平板代替电路中每部分各自的地回路;其主要原因是接地引线的感抗与频率和长度成正比,工作频率较高时将增加其共地阻抗,从而将增大由此产生的电磁干扰。工作频率在上述两者之间的可采用混合接地式。此外,还有电路的地与大地无导体连接的浮地式,该电路不受大地电性能的影响,但易受寄生电容的影响,增加了对模拟电路的差模干扰,使电路的地电位发生变化。

接地电阻应稍小,因为当有电流流过接地电阻时,其上产生的电压,将产生共地阻抗的电磁干扰。另外,该电压不仅使设备受到反击过电压的影响,而且可能使操作人员受到电击伤害的威胁。一般要求接地电阻小于4Ω。

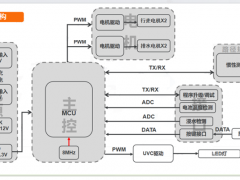

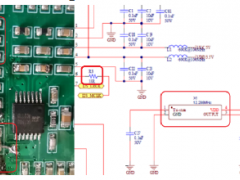

(4)电路中的电磁兼容性设计

相应于电路干扰耦合途径,电路抗干扰设计可以分为传导性耦合电磁兼容性设计和辐射性耦合电磁兼容性设计,根据电路的特征,又可分为数字电路电磁兼容性设计和模拟电路电磁兼容性设计。通常,电路由数字电路和模拟电路混合组成, 其干扰也同时包含传导干扰和辐射干扰,因而,抗干扰设计体现为一个整体的概念,需要在设计时予以全面整体的考虑。

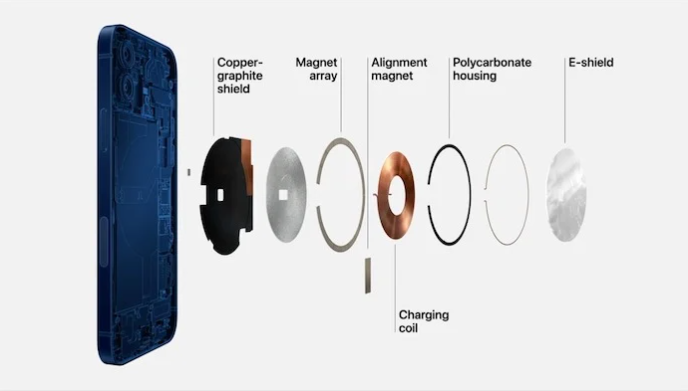

在集成电路设计过程中,在实现功能的前提下,尽量加大两个回路间的距离、缩短回路的长度和缩小回路的面积、减少回路的重合面,可减少电感性传导耦合干扰;而把易相互干扰的设备和导线在空间上尽量分离,将产生辐射干扰的设备和对辐射干扰敏感的设备在可行的前提下,在工作频率和工作时间上进行分隔、采用屏蔽的措施,使设备工况电磁场强低于允许值以及减少环线面积均可减少幅射性耦合干扰。

对数字电路, 可采取以下措施提高设备的抗干扰能力:

1)在设备工作指标允许前提下, 采用直流噪声容限高的数字电路,如CMOS数字电路的直流噪声容限远高于TTL 数字电路的直流噪声容限;

2)在设备功能设计前提下, 采用开关速度低的数字电路和低的系统时钟;

3)在系统CPU与外围I/O, 开关量输出通道中,采用光电隔离技术,防止现场电磁干扰或工频电压通过输出通

道反串到测控系统;

4)悬空的长线具有天线效应, 易于接收电磁波而产生干扰, 为此可用RC网络加以吸收, 或作不悬空接地、上拉处理;

5)采用负载阻抗匹配的措施, 消除数字信号在传输过程中,由于折射和反射的作用而产生的畸变;

6)并行的数字信号线, 如数据线、地址线, 注意负载的平衡。

对模拟电路进行抗干扰设计主要体现在电路的硬件滤波上。滤波器对于与有用信号频率不同的成分的噪音具良好的抑制能力,采用滤波网络不仅可抑制干扰源和减少干扰耦合,还能增强接受设备的抗干扰能力。总体而言,可在控制质量成本的前提下,优先选用抗干扰性能好的芯片、模块电路及高质量电源等,还可设计低噪声电路,减少带宽,抑制干扰传输,采用平衡措施等电路技术,抑制干扰。

选用适当的信号滤波器模拟电路进行噪音滤波: 其一,当干扰信号的频带高于有用信号的频带比较远时,可采用低通滤波器来滤除干扰信号;其二,当干扰信号的频带低于有用信号的频带比较远时,可采用高通滤波器来滤除干扰信号;其三,当干扰信号的频带虽略高于有用信号的频带时,可采用LC滤波器来滤除干扰信号;其四,当干扰信号的频带为不连续时,可采用选通滤波器来滤除干扰信号。针对不同干扰信号的频带和负载, 可以应用LC选通滤波器或RC选通滤波器。

7 结束语

电磁兼容性设计是一个系统的、整体的概念, 它贯穿于电子设备设计的全过程, 从开始的技术路线制定到硬件电路设计、印制电路板设计、系统软件设计再到设备的调试安装等每个环节, 它是一个系统的、完整的学科, 本文结合电磁兼容概念就硬件电路设计提出电磁兼容性设计思想。

参考文献:

[1]电磁兼容性EMC简介 2004.6

[2]徐慧君等. 单片机的抗干扰技术[J]. 电子产品世界 2004

[3]邹虹等. 数字电路抗干扰研究[J]. 数据通讯,2003

[4]吉峰. 混合信号电路板抗干扰能力和电磁兼容性[J]. 制导与引信,2003

[5]李国金等. 单片机应用系统的抗干扰技术[J]. 现代电子技术,2003

苏公网安备32050802011615号

苏公网安备32050802011615号