测控系统中模拟电路大多处理的是直流小信号,因此一般不会对外界造成明显的容性和感性耦合干扰。但也有一部分是处理交流大信号,如测角系统中的激磁电源,它是一个2 kHz的正弦交变信号,能产生变磁场,因此容易对外界造成干扰。在设计印刷板时没有有效的方法来避免板内的干扰,只能通过加大干扰回路和被干扰回路的距离来减小它的影响,或适当采用屏蔽线的方法来抑制。该控制板对其它印刷板的这种磁干扰也只能通过对整块板的屏蔽来抑制。

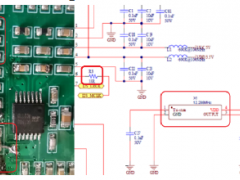

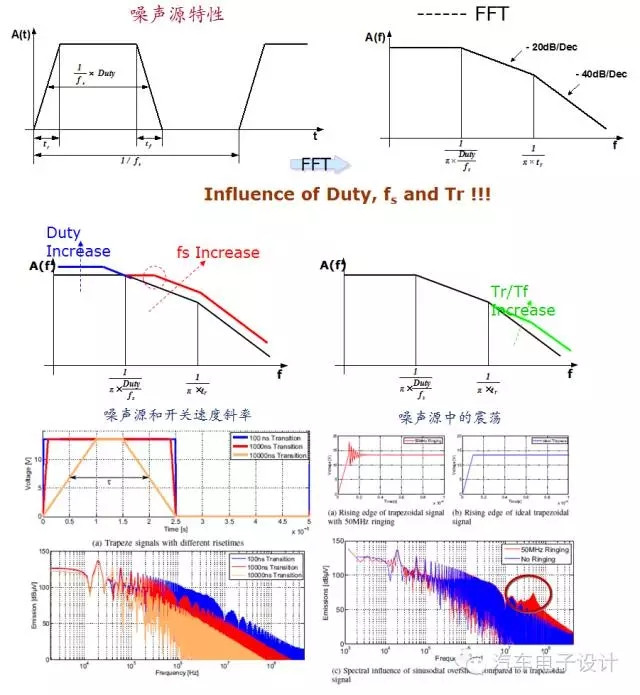

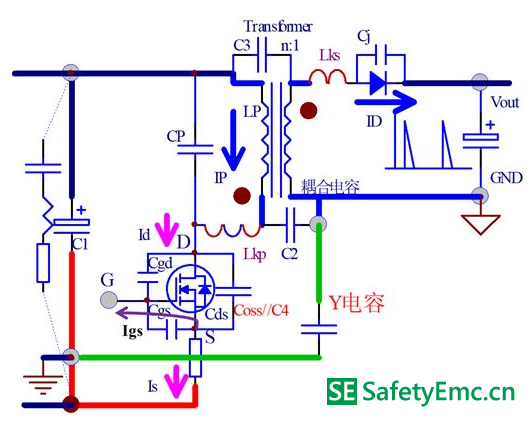

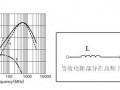

一般来讲,电子线路中大电流回路和大电压回路容易造成电感性和电容性耦合。在测试转台测控系统中,为了减小功耗,采用了数字功放。由于数字功放采用了含有高频大电压调制信号的数字PWM方式驱动,同时电机绕组又是一个电感性负载,因此它会对外界造成严重的电容性耦合干扰。但由于流过绕组的电流并不大,故它不会造成大的电感性耦合干扰。产生这种干扰的原因是驱动器中开关的通断瞬间感性负载会产生很高的尖峰电压,而容性干扰的大小同这一电压成正比。抑制数字功放的这种干扰应从以下几方面入手:

①开关二端加合理的吸收电路;

②在感性负载或A、B、C三相之间并入高压高频电容;

③在IGBT功

率开关驱动电路上设法减缓开关的导通、关断速度,使其基极驱动波形变缓,这样将使开关器件在导通和关断瞬间均有很大的压降,从而消除负载上的尖峰电压,降低其对外的电容性干扰。

以上讨论了如何在设计时消除或抑制主电路对外界的各种干扰。下面将讨论在设计主电路印刷板时如何抑制外界干扰。

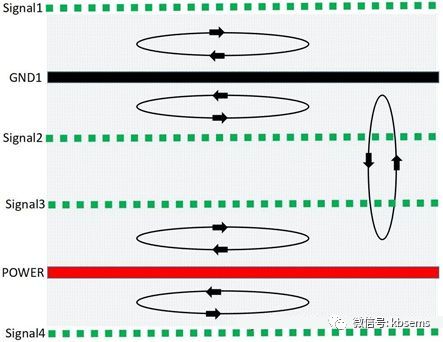

在数字电路中,传导耦合主要是通过电源和地线引入的。上面曾谈到的在Vcc-GND之间加滤波电容已从很大程度上抑制了这种耦合,因此下面主要讨论如何抑制容性和感收耦合。对于感性耦合,从设计上要避免印刷线构成环路,当然包括电源线和地线,这样既可以消除地环流,又使其不受外界磁场的干扰。对于容性耦合,要设法减小信号线之间的分布电容,因此应注意以下几点:a.尽可能避免二信号线的长距离平行布线;b.强信号同弱信号尽可能不要贴近布线;c.布线时尽量不要从管脚间穿行,对于高频信号尤其如此;d.时序逻辑电路的输入、输出线最易引入干扰,因此应避免过长引线。其输出尽量不要跨板驱动,必要时应先加缓冲隔离,如测角系统中经20 MHz分频得来的10 kHz、20 kHz等时间基准在板间传输时,应先加缓冲驱动以隔离传输线引入的回扰;e.经传输线传输的信号可能会发生畸变,因此应在下一级电路的输入处加施密特整形。

数字电路中往往会有许多引脚空闲不用,由于其缺乏确定的电平而容易引入干扰,其中时序逻辑组合比逻辑电路更易受干扰,如测角系统中的计数电路、单双稳电路等,一个干扰脉冲有可能造成其状态的误翻转。因此要将其不用的输入端依设计要求分别接至GND或通过1 kΩ电阻接至Vcc。由于时序逻辑电路的输出端可能是其内部的输入,其闲置的输出端也要避免悬空,而应对地接入1 000 Pf高频电容。

同数字电路相比,模拟电路的抗干扰问题更难解决。在数字电路中传导耦合一般不造成多大问题,但对模拟电路来讲,这种干扰却必须引起高度重视。

正如前面讲到的,传导耦合的最常见形式为公共地线耦合,而消除传导耦合的最有效的方法是一点共地。有时由于受到印刷板空间的限制不可能使每一个单元电路的地全部是一点共地(有时也不必要),因此常遵循的原则是:单元电路一点共地,然后接入公共的地线上去。这对多级线路来讲仍存在着公共地线的传导耦合,此时应注意在安排线路时不让大信号回路的电流流过小信号回路,以尽量减小大信号回路对小信号回路的干扰。例如在测角系统中激磁电源从信号发生到其输出共有多级电路,一般由运放单元电路组成,每个单元电路要一点共地,即其输入、输出及工作电源的地要尽可能从一点引出,然后连接到地母线上。在这种线路中,模拟工作的电源地线要从大信号单元电路即激磁输出级的“地”处接入,而不应在信号发生处接入。

对于测角中的粗、精反馈信号及主控系统的测速机反馈、陀螺信号的前置处理电路等模拟线路设计,除了注意以上几点外,尤其还要注意输入信号的“地”应在其多级处理线路的最前级处接入,而不应随便将输入信号的“地”接自系统任意点的“地”。由于输入端一般比输出端的信号要小,故此处遵循单元电路的一点共地原则更重要。

除上述常见的传导耦合外,模拟电路中还有其它性质的传导耦合如接触电阻变化,尤其是采用大量运放的模拟电路,由于其输入端对各种噪音比较敏感,其同、反相端尽量不要直接同可调电位器的滑动端相连(滑动端具有大的接触噪声)。

正如以上谈到的,运放的同、反相端(尤其是作为“虚地”的同相端)对噪音非常敏感,因此模拟线路中抑制电容性和电感性耦合,尤其是电容性耦合要特别注意避免这些引脚直接引入干扰。对于高增益、高阻抗和小信号放大电路更要注意这一点。

为了避免电容性干扰,连接运放的同、反相端的引线不宜过长,尤其应避免直接从前面板上的电位器一端到运放的输入端的引线。对于高输入阻抗、高增益及宽带运放电路,除了一般的措施外,还应采取同、反相端的屏蔽和其它装配工艺措施。关于这类电路的电磁兼容性设计在感应同步器前放设计中论述,此处不做详细讨论。

苏公网安备32050802011615号

苏公网安备32050802011615号