电感最低化设计

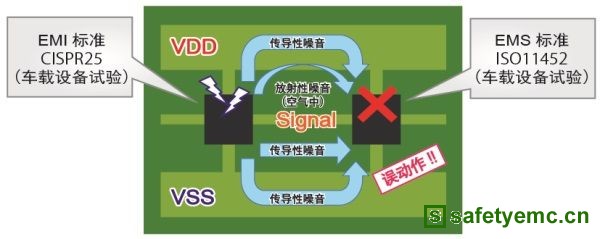

如以上的说明印刷电路板的自我电感(inductance)对高速高频电路而言,基于电路特性的考量,电路阻抗(impedance)已经成为无法忽视的问题,因为印刷pattern在高速switching时,根据计算实例6的计算结果可知,印刷pattern上会产生电压下降等问题,该电位差随着印刷pattern长度成为频率的天线,也就是说它会变成电磁噪讯的发生源。减缓电磁噪讯的方法如上所述,必需延缓电流的时间变化(di/dt),同时降低电感(inductance) ,不过基于IC特性与要求性能等限制,无法概括性决定di/dt,因此有关如何降低电感,成为所有电路共通性问题。然而电感是用物理尺寸决定,原则上缩短导线长度无法适用于所有电路,尤其是组件的位置关系,造成pattern长度变长时,要利用电感最小化减轻电感对电路的影响,往往无法顺利获得预期的效果,这种情况可在传输信号的电流loop电流方向降低实效电感,藉此减轻电感对高速高频电路的影响。

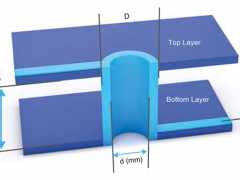

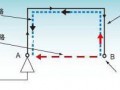

图9是两条导体内电流流动的方向,电流流动的方向相同时称为「common mode电流」(图中实线部份);电流流动的方向为相异方向时称为「normal mode电流」(图中虚线部份),电流流动方向的差异造成的实效电感Leff 可用下式表示:

电磁放射噪讯的大小并非是电感(inductance)与高频电流相乘的结果,而是电感与实效电感Leff两者相乘的积,因此降低实效电感Leff成为减轻电磁放射噪讯重要的因素,也是探讨EMI对策时的主要对象。为了降低实效电感Leff,以式(9)normal mode电流而言,可用下式表示:

L1=M 时会变成理想的实效电感,不过事实上不可能获得0Ω的实效电感。满足式(11)最大极限的条件是使相互电感M成为最大化,也就是说在相同条件下必需使实效电感最小化(图10)。

要使相互电感M成为最大化,乃是意味着使往复的电流loop作最大的磁气结合,亦即当电流loop的往复线作邻接配线时,其结果就是loop面积最小的时候(图11)。需注的是信号线与接地线一旦分开的话,就无法获得预期的实效电感,此时的实效电感大小大约是自我电感的一半左右。

Ground

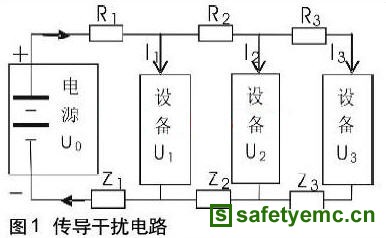

CMOS IC/LSI动作时ground流有switching电流(过渡电流),该过渡电流如果侵入电路共通阻抗(impedance)所构成的电路block时,就会成造成重大障碍,其中又以ground产生的电位差会造成机器发生误动作,并成为放射噪讯的发生源,因此长久以来一直受到高度重视,这表示降低ground的阻抗,与确保电子机器的性能具有密切的关连。多层基板是由面构成ground,所以比较容易获得近乎理想状况的低阻抗效果,双面基板时就必需设法分散ground电流并降低阻抗(impedance),基本上可以采用上述的梳形配线作对策。最后将本节介绍的重点整理成如下:

(一)减低导线pattern的长度,降低自我阻抗(impedance)。

(二)减低pattern导线的长度对降低自我阻抗(impedance)具有很好的效应。导线patte rn的宽度增加10倍,自我阻抗祇降低一半,相较之下导线pattern的长度减低一半,自我阻抗可降低1/2.2以下。

(三)将往复电流loop邻接配线,可以有效减低实效电感(inductance);减少电流loop的面积,可获得最大值的相互电感(inductance)。

(四)实效电感与电流两者相乘的积,会变成电磁放射噪讯磁界的大小。PDX安规与电磁兼容网

(五)电流loop的面积是指实际围绕信号线与接地线(return line)的面积,如果信号线与接地线未邻接贴近时,实效电感(inductance)会大幅降低。

如上所述根本上最有效的噪讯对策就是「不制造」、「不接受」噪讯,不过最近大部份的电子机器基于设计上的需要,大多是利用接口cable与外部机器、传感器连接,在静电、电界、磁界、电洞(surge)等噪讯非常复杂的环境下,接口cable会接收EMI产生诱导电压,最后造成电子机器误动作immunity等问题。为了阻隔噪讯入侵通常会在conn ector端子附近装设filter,不过接口上的EMI对策,根本方法是优先处理接口本身,残余的噪讯才用filter去除,因此接下来要介绍有关接口EMC的对策rule。

EMC的对策重点

(一).降低grand‧电源系的阻抗(impedance)

grand是电路动作的基准电位,因此基准电位稳定化非常重要,此外还必需抑制电源line的IC/LSI在switching时产生的过渡电流流动。

※数字与模拟混载电路,必需将电气性、物理性的ground‧电源系分开或是绝缘,ground的供给端需作一点接地。图12是利用相同电源驱动模拟电路与数字电路,不过实际上尽可能改采各别电源方式,提高两种性质不同的电路所需的电力,主要原因是希望避免两种电路的ground‧电源发生结合效应。

※双面印刷电路的场合为了稳定ground,因此电路板上必需设置很大的空旷面,再利用ground pattern填埋。

※由于高耗电CPU等LSI是以大电流作高速switching动作,因此可能会对周围的IC/LSI造成影响,此时可以采取Decoupling对策,或是在电源部位各别设置Filter,防止电源的高频成份流入其它电路,进而降低不良影响。

※多层基板的场合各面被分割成复数层,因此电源层属于低阻抗(impedance),高频电流会扩散至一面,如果电源与接口cable连接时,就会供给common mode电流,造成EMI更加恶化。

※Decoupling Condenser的作用是当作局部电源效应,使电源‧ground之间的电流loop最小化。

(二).避免使用over spec的高速ICPDX安规与电磁兼容网

※IC的站立与下降时间越短,相对的频率频谱范围越宽,由于放射与频率 成一定比例,而cross talk又与频率成一定比例增加,因此使的EMI对策变得非常困难,此种情况就必需严格限制使用over spec的高速IC。

※使用低耗电低电压IC,对抑制EMI的噪讯能量具有重大效益。

(三).反复周期性的高速clock电路,必需进行阻抗(impedance)整合高频电路的频率波长如果大于pattern长度所能忽视的长度时,传输线路上波形的位相与振幅就会对电路造成影响,最后导致linking over shoot等现象,因此反复周期性的高速clock电路,必需进行阻抗(impedance)整合。

※因linking造成的偏斜波形,是发生放射与cross talk的主要原因之一。

※无终端时反射系数如下式所示:

p=(ZR-ZO)/(ZR+ZO)----------------------------(12)

如上所述最有效的终端法是并列终端与Tabnan终端,不过这两种方式最大缺点是DC成份的耗电性偏高,很容易造成驱动端IC过度负担。

※虽然直列终端的设有终端电阻,不过即使收信端发生反射,也不会使驱动端产生再反射,而且这种方式的damping电阻通常祇有数十Ω左右。

(四).为减缓cross talk,必需增加信号pattern之间的结合阻抗(impedance)虽然具体方法是扩大物理间隔,不过实际上大部份的电路板并无充裕的空间,因此建议下列替代方法:

※由于cross talk的大小随着并行pattern的长度增加,因此建议尽量缩短高速信号pattern的长度。

※在复数并行的信号pattern之间设置ground pattern,除此之外增加电路板上的输出入line长度,可获得相当好的效果。

(五).高频电路的组件layout,要求短pattern导线,因此必需优先检讨组件的layout

※长度很长的并行pattern导线,在信号pattern导线之间设置与ground相同电位的pattern导线。

※利用cable与LCD连接时,必需避免造成ferrite core尺寸与loop面积过大。

※电路必需平衡化,具体而言就是抑制电路与ground层的阻抗(impedance),并使信号source端、return端与ground的阻抗(impedance)变成一致。

(六).电源‧ground层的对策

降低由于电源‧ground层的阻抗(impedance),主要目的是要抑制电源‧ground层的噪讯(noise),尤其是随着系统clock高速高频化,高频电流祇会在导体表面流动(简称为pattern的表皮效应),造成导体的阻抗变高,如果高频电流流入具有阻抗的导体,就会产生电下降的问题,有鉴于此必需设法形成一个接近理想状况的ground层,使电路的基准电压即使是高频电流,也不会产生电压变化,换句话说ground层的低阻抗化,乃是最有效的噪讯对策。低阻抗化具体方法是减轻表皮效应,同时扩大平面(plain)的面积,使电感(inductance)最小化。利用多层电路板构成电源‧ground层的高频电路,虽然无法达成相同电位的理想状况,不过却是实现高可靠性、高noise margin系统不可欠缺的要素,除此之外多层电路还具备下列优点:

※利用ground面(plain)与信号线之间形成的容量与输出IC的输出阻抗(impedan ce)时定数,使数字波形迟钝化进而抑制多余的高频波成份的强度(level)。PDX安规与电磁兼容网

※在信号线下

※可以降低特性阻抗(impedance),由于信号线与ground两者结合后会变的很大,因此可以抑制cross talk。

※信号线与grand两者所形成的loop面积,相对的可以缩小。降低电源层的高频电流,可将Decoupling Condenser以Filter

苏公网安备32050802011615号

苏公网安备32050802011615号