摘要:随着电子技术的飞速发展,高密度、高频率的电子产品迅猛增长,势必导致电磁环境的进一步恶化,从而引起一系列的电磁兼容问题。本文以电磁兼容为主线,以消除各部分电路之间的干扰、降低印制电路板(PCB)的传导发射和辐射发射为目的,对PCB 的抗干扰设计进行了综合分析,确保产品顺利通过电磁兼容测试。

关键词: 印制电路板 电磁兼容 布局 布线 静电防护

1 引言

电磁兼容(EMC)指的是一个产品和其他产品共存于特定的电磁环境中,而不会引起其他产品或者自身性能下降或损坏的能力[1],即产品和其他产品能够“和平共处”,彼此间的电磁干扰(EMI)不会影响产品的正常工作。引起电磁干扰的原因是多方面的,主要可归结为过高的工作频率或不合理的布局布线。在高频化趋势不可避免的情况下,一个好的PCB 设计,应着重从元器件布局、时钟电路设计、电源设计、接地设计、静电防护设计等方面进行综合考虑。

2 整体布局布线设计

2.1 整体布局

整体布局是PCB 设计的第一步,合理的布局不但可以增加PCB 的视觉美感,还可以提高产品的电磁兼容水平,一般来说,器件的整体布局应遵循以下原则:

(1) 围绕各功能电路的核心元件进行布局,保证各元器件沿同一方向整齐、紧凑排列,易受干扰的元器件不能相邻布置,以防止信号间耦合;

(2) 处理敏感信号的元件要远离电源、大功率器件等,并且不允许敏感信号线穿过大功率器件,热敏元件应远离发热元件,温度敏感元件宜置于温度最低的区域;

(3) 加大具有高电位差元器件之间的距离,防止它们放电而引发短路,并可在无铅时代减少CAF(Conductive Anodic Filament)发生的可能性。同时,高电压元器件应尽量布设在调试时手不易触及的地方,并加以绝缘保护;

(4) 对于高频电路,推荐采用菊花链布线或星形布线,并且高速数字信号应布置在与地线相邻的信号层,并且信号线尽可能短;

(5) 一个过孔会带来约0.5pF 的分布电容[2],因此,减少过孔数量可显著提高运行速度。

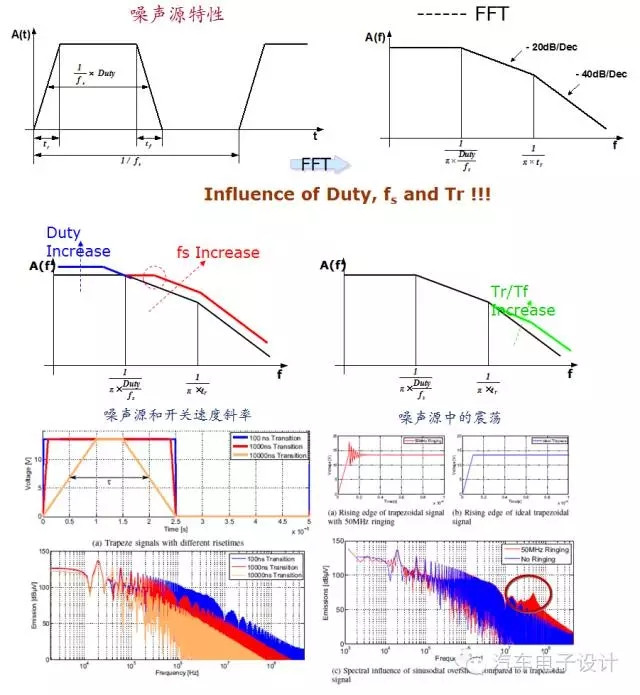

2.2 元器件的选择和布置

相比于分立元件,集成电路元器件具有密封性好、焊点少、失效率低的优点,应优先选用。同时,选用信号斜率较慢的器件,可降低信号所产生的高频成分,充分使用贴片元器件能缩短连线长度,降低阻抗,提高电磁兼容性。另外,应优先选用供应渠道稳定的元器件,以确保生产加工的连续进行。

元器件布置时,首先按一定的方式分组,同组的放在一起,不相容的器件要分开布置,以保证各元器件在空间上不相互干扰。另外,重量较大的元器件应采用支架固定。

2.3 PCB 的选取和分层

印制板大小应适当,太大,成本增加;太小,散热困难,且相邻线间易串扰。推荐的PCB 形状为长宽比约3:2 的矩形[3]。

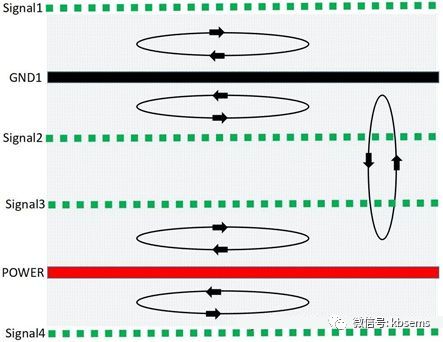

在时钟频率超过5MHz 或上升时间小于5ns 的高频电路[4]中,使用多层板能大幅降低PCB 体积和减小电环路面积,从而有效降低电磁干扰。PCB 分层时要确保信号线有相邻完整的映像回流平面,同时,为方便电源解耦,电源层应紧邻地层且在地层下面。根据以上原则,对于四层板,推荐的分层方法为:信号层、地层、电源层、信号层。六层板推荐的分层方法是信号层、地层、信号层、电源层、地层、信号层。

2.4 整体布线

PCB 布线总的原则是先布时钟、敏感信号线,再布高速信号线,最后布一般的不重要信号线。

布线时,在总的原则前提下,还需考虑以下细节:

(1) 在多层板布线中,相邻层之间最好采用“井”字形网状结构;

(2) 减少导线弯折,避免导线宽度突变,为防止特性阻抗变化,信号线拐角处应设计成弧形或用45 度折线连接;

(3) PCB 板最外层导线或元器件离印制板边缘距离不小于2 mm,不但可防止特性阻抗变化,还有利于PCB 装夹;

(4) 对于必须铺设大面积铜箔的器件,建议用栅格状[5],并且通过过孔与地层相连;

(5) 短而细的导线能有效抑制干扰,但太小的线宽会增加导线电阻,导线的最小宽度可视通过导线的最大电流而定,一般而言,对于厚度为0.05 mm,宽度为1mm 铜箔允许的电流负荷为1A。因此,1-1.5mm 的线宽完全可满足要求,对于小功率数字集成电路,选用0.2-0.5 mm 线宽即可。同一PCB 中,地线、电源线宽应大于信号线;

(6) 为减少辐射,利用静电屏蔽原理[6],对于敏感元件端头可采用如图(1)所示的抗干扰保护环,并对保护环采用单点接地设计,不接地的保护环是起不到屏蔽作用的。

图1 抗干扰保护环

3 传输线设计

端接匹配的好坏是传输线设计能否达到最佳性能的关键。只有当电路终端负载等于特性阻抗

时,传输的信号才会在远处被充分吸收,否则,部分信号将被反射回来,造成逻辑混乱或失真。

当走线终端存在集总线型负载或单一元件时,选用串联电阻源端匹配可以使阻尼振荡和反射效应达到最小。对于具有分布式负载的走线终端,选用并联电阻终端匹配,可得到几乎不失真的波形。并联端接的缺点是消耗较多的功率,因此,对于电池供电的便携式产品,应避免使用并联终端。

4 时钟部分设计

合理布局时钟系统是EMC 设计的关键,不合理的时钟布局会导致PCB 板不能稳定工作。

在设计时钟系统时,时钟晶体和相关电路应与其他电路分开并布置在PCB 的中央位置,特别注意

时钟发生器的位置尽量不要靠近对外的连接器。必要时在时钟晶体下铺设地层,有利于散热并可将振荡器内部产生的射频电流泄放到地平面上。时钟线和高速信号线尽量走内层,并夹在两个地平面层中间,以确保相邻完整的回流路径。对于高频时钟布线,要求尽量减小传输线长度,降低传输线效应。

苏公网安备32050802011615号

苏公网安备32050802011615号