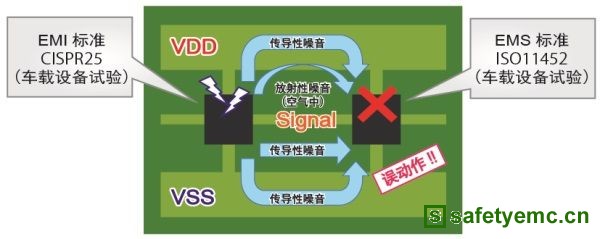

3 EMC设计对策

在进行EMC设计时,考虑到反激式多路输出电源电磁干扰以及电源包括两组子系统的特点,EMC设计应贯穿于实验、设计、调试的始终,包括项目设计前预先考虑到的措施,实验中遇到问题后有针对性地采取的措施,以及经过比较的其它方案。

3.1 减弱差模辐射耦合

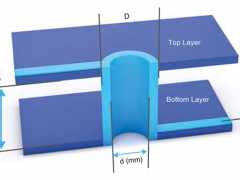

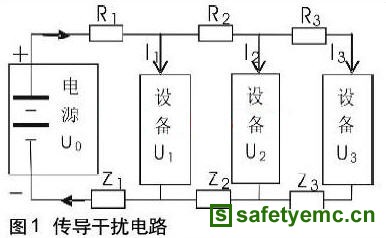

如图2所示,耦合途径为寄生磁耦合电感M通过干扰源产生的噪声磁场与被干扰回路发生磁通铰链而形成。设噪声磁场的磁通密度为B,穿过一个闭合面积为S的回路,则在该回路感生出干扰电压e,即

e=-(d∫BS)/dt(4)

式中:B和S均为矢量。

结合式(1)及式(4)容易推得,寄生磁耦合电感M与涉及的干扰回路面积S成正比例关系。在图2中,存在有较大的di/dt的回路主要包括变压器输入侧环路S0,二次侧环路S1和S2以及驱动环路S3。

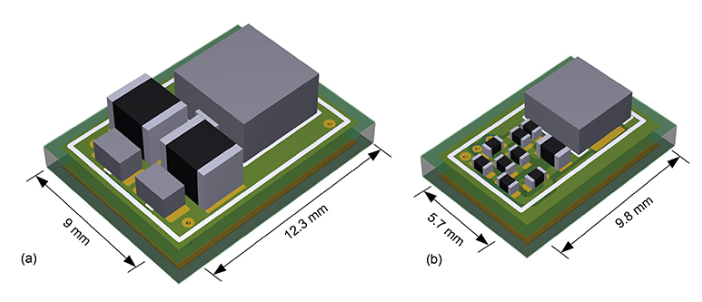

仔细设计电路板走线,尽可能减小上述回路的围绕面积。将高频去耦电容Cd0尽量靠近变压器原边和MOS管,Cd1尽量靠近负载,以求减小围绕面积S0与S2,并且要求Cd0和Cd1是低ESR和低ESL的电容器。

电源输出端至负载的引线应尽可能地短,而且多路输出每一路都要使用双绞线,因为,相邻绞环中在同一导体上产生的电动势方向相反,相互抵消,这对电磁干扰起到较好的抑制作用。

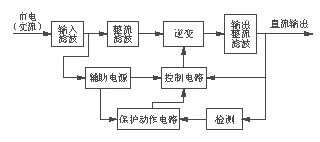

3.2 减弱共模辐射耦合

参照图3,由式(2)可得,共模电流Icm1及Icm2的幅值与两电气节点①与②处dv/dt和对PE(安全地)的分布电容Cd1和Cd2的积成正比。图中节点①是MOS管漏极与变压器原边的连接点,节点②为变压器二次侧与输出二极管的连接点。共模电流辐射强度与共模电流围绕回路面积有关,也就是说,电磁辐射强度和电流环路面积成正比,这里环路面积用阴影面积表示。因此,减弱共模辐射耦合应从3个方面入手,即减小dv/dt;减小分布电容;减小共模电流环路面积。

节点①及②存在非常大的电压瞬变,因而在节点①及②处布线应当占用尽可能小的面积,以减小分布电容值。分布电容一般为pF级,因而在低频段(<1MHz)其阻抗影响非常显著,需要滤波器对共模电流进行衰减,共模扼流圈电感值一般取10~100mH。

苏公网安备32050802011615号

苏公网安备32050802011615号