文献[11]对插值公式另有推导,并给出了求谐波幅值、相位时不同于基波的修正公式。文献[6]给出了加 blackman-harris窗的插值公式,求解过程中涉及解高次方程的问题。另外,窗函数为矩形窗或汉宁窗,采用插值公式对计算结果进行修正时,采样窗口的宽度不得低于8个基频周期,所以,这种算法需要很大的数据存储空间。

3.1.2 硬件同步技术

利用锁相环使信号频率和采样频率同步

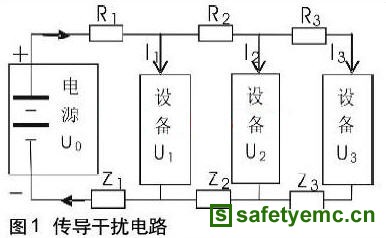

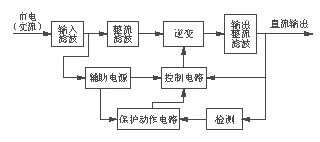

图3 锁相环工作原理图

这是一种最传统也是最直接的措施。锁相环包括三个基本部件:鉴相器(PD),环路滤波器(LF),压控振荡器(VCO),工作原理如图3所示。鉴相器是相位比较器,它把输入信号和VCO的输出信号的相位进行比较,产生对应于两信号相位差的信号,环路滤波器滤去误差电压中的高频成分和噪声以保证环路所要求的性能,增加系统的稳定性,输出受控电压,使压控振荡器的频率向输入信号的频率靠拢,也就是使差拍频率越来越低,直至消除频差而锁定。实际装置的采样电路中锁相环先将采样信号(系统电压、电流)的基频N倍频,并以其作为产生采样脉冲的基准时钟,再根据周期采样点数的要求,对该基准时钟进行记数分频,这样就可得到能够自动跟踪输入信号基频的等间隔的采样脉冲信号。

这种方法的实时性好,硬件电路复杂,硬件成本较高。

3.1.3 软件同步技术

3.1.3.1 软件同步采样

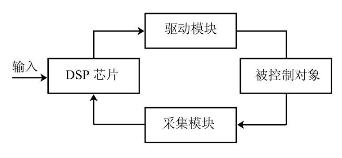

其基本实现框图如图4所示:

图4 软件同步采样实现框图

输入信号首先经窄带滤波器,滤除50Hz以外的谐波成分,以免信号波形中的尖角、毛刺使过零比较器误动作,然后信号经过零比较器,把正弦波信号变成方波信号输出,再经波形锐化环节,将方波的上升沿和下降沿锐化,然后送给CPU。当检测到信号的上升沿时,申请中断。两次中断之间的时间间隔就是信号的实际周期。用该周期除以预制的每周期采样点数,就可以计算出两个采样点之间的时间间隔,通过软件设置采样同步脉冲,从而达到动态跟踪系统的频率变化,适时刷新采样的时间间隔,实现同步采样的目的。

DSP技术的发展,使这种同步采样方式获取上升沿的时刻更为方便,计算出的采样周期也更为精确。只是消除信号中的抖动,避免过零比较器误动作,是这种采样方式要解决好的技术问题。

3.1.3.2软件测频法

DSP芯片的发展,为各种计算量比较大的算法的实施提供了条件,利用软件计算系统实际频率的方法,也在实际应用中获得了一席之地。而且采用软件的方式,不需添加任何硬件,可以降低成本,简化硬件电路的设计,减小装置的体积。这种方法的一般思路是先对采样数据进行FFT或加窗FFT运算,根据计算结果得到采样频率与基波频率的失步偏差,再用该偏差值修正采样频率,达到自适应调整采样率的目的。下面简单介绍两种:

1) 用加海宁窗的FFT插值算法求电力系统基波频率[4]。信号在满足香农(Shannon)采样定理的条件下以频率对其进行采样。当不是基频的整数倍时,基频信号的频率可表示为

(9)

(9)

式中N为采样点数;d0位小数;N为每周期采样点数。设经加窗FFT之后,在基频(50Hz)附近最高的三条谱线分别Y0、Y1、Y2,则d0可由下式得出:

(10)

(10)

将上式代入(9)式中即可求得精确的基波频率,然后对下一周期的采样频率进行修正,即可实现频率跟踪的目的。

这种方法在分析结果的同时,附加少量运算,达到了对采样频率进行修正的目的,而且加窗插值算法本身对非同步误差就有修正作用,理论上讲是比较理想的。

2) 用FFT结果求相位偏差对采样频率进行修正[6]。

这种方法每采一个点就要进行一次FFT运算,然后求得某一个被分析信号上一个分析窗口(第N-1个)与本次分析窗口(第N个)之间的相位差,由此得到此时的系统频率为:

(11)

(11)

然后,根据计算结果对下一个采样周期进行调整。

由以上分析过程可以看出,这种方法的计算量是相当大的,采样频率比较高时(比如6.4kHz及以上)一般的芯片是不能承受的。所以只适合采样频率比较低的情况。

苏公网安备32050802011615号

苏公网安备32050802011615号