3.1 各级架构

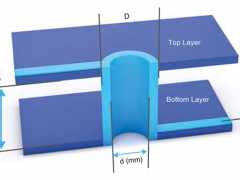

此低通滤波器中,总共大致可分为3个架构,如图3.3所示。其中包括有边界处理器(Boundary)、内存(Memory)、计算处理器(Processer)等。一一叙述如下。

图3.3 內部架构示意图

3.1.1 边界处理器

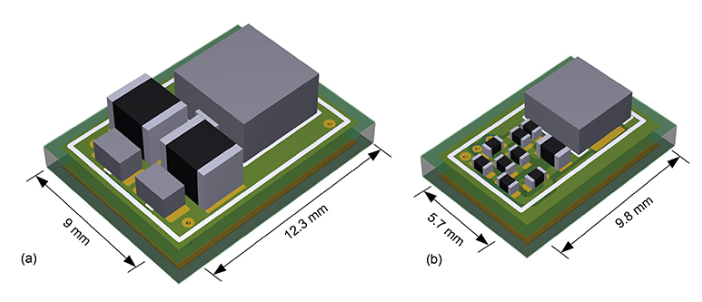

为了图像在边界延伸时的特殊情况,我们设计了一个专门用来处理边界问题之部分,如图3.4。

图3.4 边界处理器

边界处理器之规格如表3.2所列。DIN_1、DIN_2及DIN_3仅含有YU或YV,因此为16位。DOUT_1、DOUT_2、DOUT_3、DOUT_4及DOUT_5仅含有Y或U或V,所以为8位。C_EVEN是为了控制内存的读写动作,所以会把C_EVEN接至内存的输入脚。

表3.2

3.1.2内存

我们把偶数列跟奇数列的数据分别储存于不同的内存中。先使用Memory Generate 呼叫出 single port的SRAM,然后与控制读写电路组合成如图3.5所示之内存,偶数列与奇数列的内存架构一样,只有控制读写电路略有不同。

表3.3

本章开头提到为了节省内存空间,因此在存入数据时,并非将原始的数据直接存入,而是只取YU或者是YV,加上一次储存两行的数据,所以输入及输出数据为32位。

3.1.3 计算处理器

计算处理器的主要功能是要处理对Y做加权函数的计算。DIN_1与DIN_3的加权值为1,而DIN_2的加权值为2。

整理出计算处理器规格如表3.4。

表3.4

苏公网安备32050802011615号

苏公网安备32050802011615号