3 集成电路电磁兼容性设计方法研究

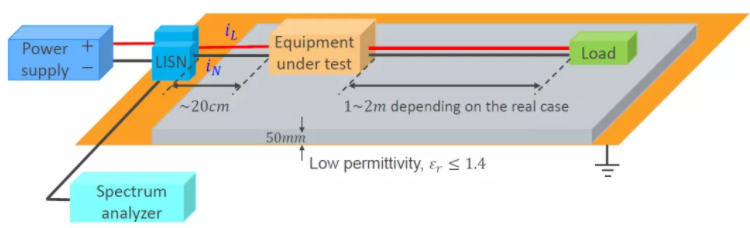

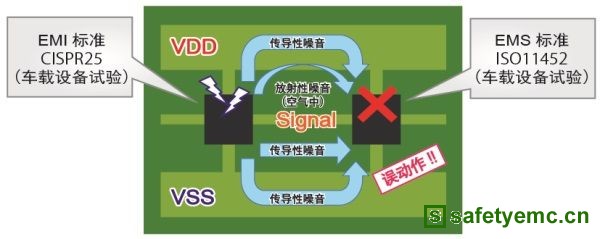

集成电路电磁兼容性的研究不仅涉及集成电路自身的电磁发射、抗扰动测试和设计方法研究,而且有必要和集成电路的应用相结合,将强制性标准对设备和系统的电磁兼容要求结合到集成电路的设计中,使得更易于设计出符合标准的最终产品。

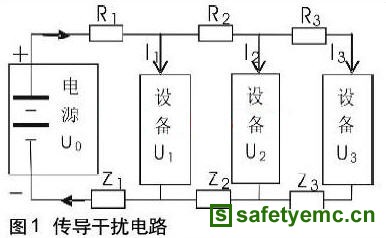

目前,集成电路的工作频率已达到吉赫兹,上升、下降时间仅为几皮秒。高传输速率以及电路复杂性的增加,使得如果设计不合理,IC将会产生较大的电磁发射和传导发射,同时抗扰动能力也会下降,致使现代电子产品将无法满足EMC要求,这也是当前集成电路设计工程师们所面临的难题:要求集成电路既具有低的电磁发射,又具有高的抗干扰能力。根据上述对集成电路设计所提出的要求,本文列出了下面几种集成电路电磁兼容性设计方法。

3.1 降低集成电路电磁发射的设计方法

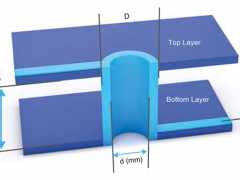

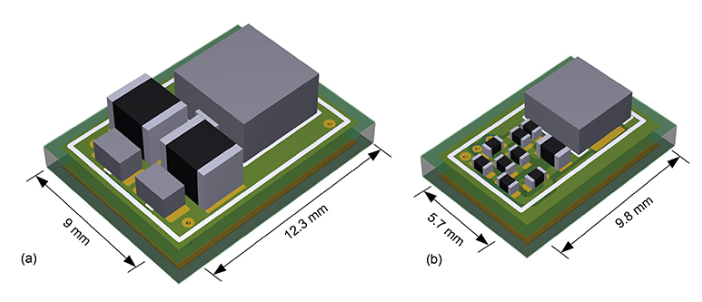

元件的电磁发射与制造工艺、封装、开关门数、I/O口和数字同步核心模块等的参数有关。减小电磁发射最重要的是要控制供电通路的阻抗,具体的措施如下。(1)减小寄生电感。(2)采用合适的电源策略。(3)增加去耦电容,已证明增加大的嵌入电容(1 nF~50 nF)可以有效地减小辐射发射。嵌入大电容的方法是:在最大耦合作用的每个电源和地环路的上方放置片上去耦电容,并且在布线通道下面的空间连上结电容,通常薄栅介质电容或金属-绝缘体-金属电容可以产生大电容(几纳法)。(4)电源线、地线上增加小的串联电阻。(5)核心电路模块和I/O区分开,并独立供电。(6)采用异步设计。来自数字电路的噪声与该模块是同步设计的本质有关,可以通过控制时钟信号波形,扩展频谱来减小电路的电磁发射,另一种方法是集成电路核心模块采用异步设计,异步电路所产生的电磁辐射比同步电路要小得多。(7)仔细设计外部和芯片的版图。例如,采用双绞线的差分输出信号产生的电磁发射(EME)较低,且不易受EME的影响。(8)直接在电路或封装级采用吸收材料,比如采用铁氧体,特别是频率在300 MHz以上发射频谱包络可以减小3 dB~20 dB。

3.2 提高集成电路抗扰动度的设计方法

提高集成电路的抗扰动度,即减小集成电路的电磁易感性(EMS)。整流/泵、寄生元件、电流及功耗太大是EMS的4个最主要干扰效应。将EMS效应减到最小的主要办法如下。(1)通过特殊的设计可以提高集成电路的抗扰动能力,如施密特触发器。(2)采用差分电路拓扑和版图设计使电路设计匀称,避免可能出现的整流现象。在频率范围为1 MHz~10 MHz,这种方法可以将电路的抗扰电平从1.5 V提高到5 V;(3)通过滤波限制进入敏感器件的频率范围;(4)采取高共模抑制比(CMRR)和电源抑制比设计(PSRR)也可以使电路免受整流干扰,并保持内部节点阻抗低且所有敏感节点都在片上。(5)采用保护器件将大于所要求的EMS抑制电平的部分钳位掉是很重要的。(6)异步电路、增加片上电容也可以改善电路的抗扰度[6]。

对于微电子学行业来说,集成电路电磁兼容性的描述已经成为一个非常重要的主题。实际上,如果不对集成电路电磁辐射及抗扰度方面进行深入研究,就很难满足电子设备电磁兼容性方面的要求。随着工作频率及芯片复杂度的不断增加,具有低电磁辐射和高抗干扰度的集成电路设计研究具有非常重要的意义。

参考文献

[1] 郭淑霞,董中要,张宁,等.北斗卫星导航接收端抗干扰性能测试系统构建方法研究[J].计算机科学,2013,40(7):28-29.

[2] 大卫A.韦斯顿.电磁兼容原理与应用[M].杨自佑,王守三,译,北京:机械工业出版社,2006.

[3] 路宏敏,余志勇,李万玉.工程电磁兼容[M].西安:西安电子科技大学出版社,2010.

[4] BEN DHIA S, RAMDANI M, SICARD E.集成电路的电磁兼容——低发射、低敏感度技术[M].王宏博,孙倩,李炜,等,译.北京:电子工业出版社,2010.

[5] 黄明华,周耀坤.电磁兼容在集成电路中的设计应用[J].机电工程技术,2005,34(10):62-64.

[6] RAMDANI M, SICARD E, BOYER A, et al. The electromagnetic compatibility of integrated circuits-past, present, and Future[J]. IEEE Transactions on Electromagnetic Compatibility, 2009, 51(1):78-96.

作者简介:王媛媛1.西安科技大学 电气与控制工程学院,陕西 西安 710054; 张 凯2.中国空间技术研究院 西安分院

苏公网安备32050802011615号

苏公网安备32050802011615号