摘 要:分析了静电放电( ESD) 保护的基本原理,指出了传统的用于模拟电路的ESD 保护电路在高速电路应用中的局限性。 提出了在端口的栅极接地NMOS 管和栅极接电源PMOS 管的基础上,加上电源与地之间的高速静电泻放回路(片上保护) 的新电路结构。 仿真结果表明,该电路满足USB2.0 高速接口电路的ESD 保护要求。 试验测试结果表明该ESD 保护电路在人体模式下的击穿电压在正负2 500 V 以上,具有实际的应用意义。

关键词:静电放电保护; 人体模型; 片上保护; 栅极接地的NMOS

随着超大规模集成电路工艺技术的不断提高,目前CMOS 集成电路已经进入了超深亚微米阶段,MOS 器件的尺寸不断缩小,栅氧化层厚度越来越薄,其栅耐压能力显著下降,集成电路失效的产品中有35 %是由于ESD 问题所引起的。 因此CMOS 集成电路的静电放电( Elect rostaticDischarge , ESD) 保护电路的设计越来越受到了电路设计者的重视。

ESD 保护电路是为芯片电路提供静电电流的放电路径,以避免静电将内部电路击穿。 由于静电一般来自外界,例如人体、机器,因此ESD 保护电路通常在芯片的压焊盘( PAD) 的周围。 输出压焊盘一般与驱动电路相连, 即与大尺寸的PMOS 和NMOS 管的漏极相连,因此这类器件本身可以用于ESD 保护放电,一般情况下为了保险,输出端也加ESD 保护电路;而输入压焊盘一般连接到MOS 管的栅极上,因此在芯片的输入端,必须加ESD 保护电路。 另外,在芯片的电源(Udd ) 和地(Uss ) 端口上也要加ESD 保护电路,以保证ESD 电流可以从Udd安全地释放到Uss。 作者在传统的模块电路ESD 保护电路的基础上提出了应用于高速模拟电路的ESD 保护电路。

ESD 保护电路原理分析

数字电路一般采用两级保护电路,并且在主保护电路和次保护电路中串联一个限流电阻,而大的限流电阻和ESD 钳位器件的节电容会产生一个大的RC 延迟,因此,不适合应用于高速模拟CMOS集成电路中。

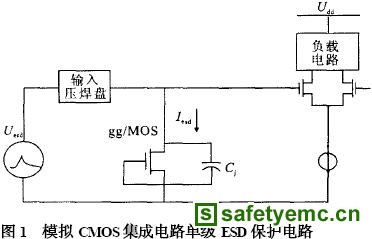

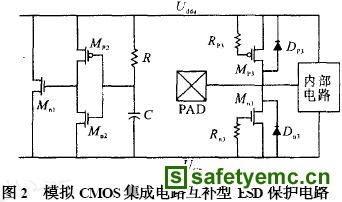

图1 是CMOS 模拟集成电路单级ESD 保护电路。 ESD 钳位器件是栅极接地的NMOS 管(ggNMOS) 。 为了承受较大的ESD 电流,ggNMOS管设计成很大的尺寸,导致大尺寸的ggNMOS 管以及大的漏极PN 扩散结在输入端上形成了大的漏极寄生电容。 由于PN 寄生电容是非线性的可变电容,而高精度的高速模拟集成电路要求输入端寄生电容为常数,因此ESD 钳位器件的寄生电容是高速模拟集成电路的一个主要误差来源。 另外,当静电压通过模拟信号管脚直接加在运算放大器的两个输入端或者加在以共源形式连接的差分对管的栅极时,极高的静电压很容易将MOS 管的栅氧化层击穿。 此时单个的ggNMOS 管无法起到保护作用。因此, Ket 等人提出了用ggPMOS 和ggNMOS管一起组成ESD 保护电路,如图2 所示,其中Dp3 、Dn3各为Mp3 和Mn3 管漏区的寄生二极管。

图2 左半边为嵌位(Clamp) 电路,当PAD 上被加上正的ESD 电压时,RC 检测电路经过一个反相器来触发Mn1 管,将大的ESD 电流通过大尺寸的Mn1管释放到Uss 。 但是该电路的局限性在于不能有效的释放负电压下的ESD 电流。 并且由于RC 的值对电路能否正常工作至关重要,所以对其精度要求较高,而R、C 的实际工艺误差较大。