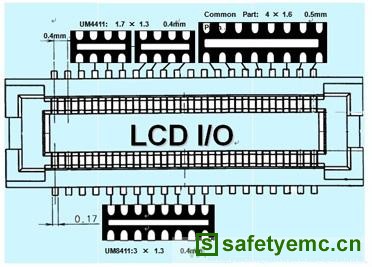

图4(b)是电容耦合技术应用于输入级ESD防护电路上的一种安排,GCNMOS(Gate-Couple NMOS)是ESD电流旁通用的器件,尺寸较大。

因应用在输入端,故其栅极需经电阻Rg(~10 kΩ)接地,以使该GCNMOS在CMOSIC工作时是关闭的。另有-NMOS连接成电容状Cc加强电容耦合作用。当有正的ESD电压在输入PAD上发生时,一部分的正电压会经由Cd与Cc耦合到GCNMOs的栅极,栅极电压会经由Rg放电到地去,Rg的大小会影响栅极电压的维持(Holding)时间。GCNMOS因而可以达到均匀导通的目的,以提升其ESD防护能力。

3 结 语

MOS集成电路ESD保护电路基于工艺级别、器件级别和电流级别的改进,已有大量优秀的ESD保护电路出现,ESD保护电路强度已超过2 000 V(采用HBM模型试验)。几种方法结合制造的ESD保护电路,如采用栅耦合PTLSCR/NTLSCR ESD保护电路,可有效的对深亚微米CMOS IC薄栅氧化层保护,而且占用的版图面积只占传统ESD保护电路的1/2左右。

苏公网安备32050802011615号

苏公网安备32050802011615号