一种众所周知的ESD能量抑制技术是在电路的关键部位使用瞬变抑制二极管。这样的器件基本上是快速响应的电压箝位器件。当ESD或其它因素产生一个过压瞬变脉冲时,瞬变抑制器就按照其额定值将电压箝位于一个安全电压值,以保护瞬变抑制器后面连接的器件。应根据器件能承受的预计瞬时功耗,仔细地选择瞬变抑制器的功率承受大小。

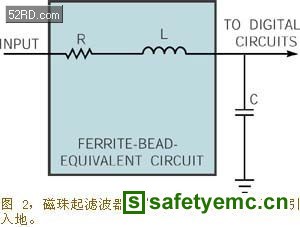

一种可在电路输入级使用的简单的ESD瞬变抑制技术,就是将一个磁珠串在输入引线上,并在输入引线和地之间接一只容量很小的电容器。图2示出了磁珠的等效电路。输入端的LC电路起滤波器的作用,将ESD瞬变的能量分流入地。当使用瞬变抑制二极管保护任何输入端或输出端时,要使瞬变抑制器尽量靠近这些端子。很长的导线和电路板印制线都有寄生电感,当ESD瞬变脉冲进入电路时,寄生电感就会产生电压过冲与振铃问题。

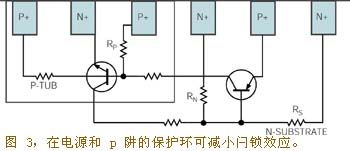

你可使用CMOS布局技术来防止闩锁效应,因为CMOS布局技术可监控ESD瞬变会进入器件的各部位:器件的电源引脚、输入引脚和输出引脚。你应降低晶体管(PNP和NPN)的增益,并提高闩锁效应的阈值,方法是加大器件结构中P沟道Tub与P沟道漏极之间的间隔。在电源和p-tub上连接p+和n+保护环也可以降低晶体管增益,提高闩锁效应的阈值(图3)。防止闩锁效应的其他工艺技术有:提高阱深度以减少寄生晶体管的增益;采用绝缘衬底(如蓝宝石硅)以降低tub和衬底中的电流,;在每个阱下面采用埋层或外延层(图4)。

你也可以用良好的电路设计技术来减少ESD危害和与ESD有关的电子器件失效。元器件选用得当和关键部位使用电路级技术(保护网络)均可减少ESD的种种影响。良好的接地与电路板布线技术;在装配、生产和测试时小心取放对ESD敏感的器件;在包装和运输器件和组装电路板时采用适当的防静电包装材料,这些措施都可减少失效。电路屏蔽得当也可以减少ESD的影响。

苏公网安备32050802011615号

苏公网安备32050802011615号