对数字集成电路,从电磁兼容性角度看,应多选用高噪声容限的CMOS器件代替低噪声容限的TTL器件。

尽量使用低速、窄带元器件和电路。

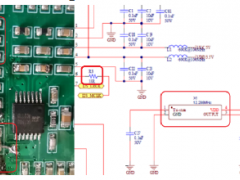

选用分布电感较小的表面贴装元器件(SMD),选用高频特性好、等效串联电感低的陶瓷介质电容器、高频无感电容器、三端电容器和穿心电容器等作滤波电容。

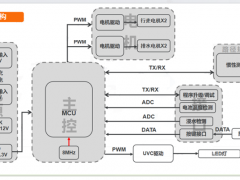

3.10控制电路及PCB的电磁兼容设计

信号地是指信号电流流回信号源的一条低阻抗路径。在设计中往往由于接地方法不恰当而产生地环路干扰和公共阻抗耦合干扰。因此,要合理选用接地方式,接地的方式有单点接地、多点接地和混合接地。

1)地环路干扰常发生在通过较长电缆连接,地相距较远的设备之问。原因是由于地环路电流的存在,使两个设备的地电位不同。通常用光电耦合器或隔离变压器进行“地”隔离,消除地环路干扰。由于隔离变压器绕组之间寄生电容较大,即使采取屏蔽措施的隔离变压器通常也只用于1MHz以下的信号隔离,超过lMHz时多采用光电耦合器隔离。

2)公共阻抗耦合当两个电路的地电流流过一个公共阻抗时,就会发生公共阻抗耦合。由于地线是信号回流线,一个电路的工作状态必然会影响地线电压,当两个电路共用一段地线时,地线的电压就会同时受到两个电路工作状态的影响。可见无论是地环路干扰还是公共阻抗耦合问题都是由于地线阻抗引起的,因此,在设计时一定要考虑尽量降低地线阻抗与感抗。

3)减小控制电源噪声电源线上有电流突变,就会产生噪声电压。在靠近芯片的位置增加解耦电容,能有效减小噪声。如果是高频电流负载,则采用多个同容量的高频电容和无感电容并联能获得更好的效果。注意电容容量并非越大越好,主要根据其谐振频率、提供脉冲电流频率来选择。

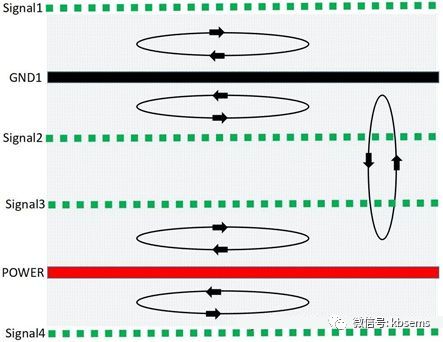

4)印制板的合理布线印制板合理地布置地线将能有效地减小印制板的辐射以及提高其抗辐射干扰能力,请注意以下几条。

布置地线网络,即在双面板的两面布置最多的平行地线。

对于一些关键信号(如脉冲信号和对外界较敏感的电平信号)的地线的布置必须尽量缩小引线长度,减小信号的回流面积,如果是双面板,地线和信号线可以在印制板两面并联平行走线。

若是多层线路板,且既有数字地又有模拟地,则数字地和模拟地必须布置在同一层,减小它们之间的耦合干扰。

在实际电路中常发生公共阻抗耦合,因此,要根据实际情况选择正确的接地方式。

3.11其他方法

1)给IGBT、MOSFET等开关器件的驱动信号增加一个-5V~-10V的负电平,可提高驱动信号的抗干扰能力,或驱动信号采用光纤传输,光纤适宜于远距离传输,具有抗干扰能力强的特点。

2)为了防止电平信号中的毛刺,引起软件的误判断及误动作,可以通过多次采样等数字滤波技术来滤除干扰信号。

4结语

本文详细分析了隔离式DC/DC变换器存在的电磁干扰源及其产生机理,并详细介绍了针对其主电路和控制电路的电磁兼容设计方法,这些方法对其它电子产品的电磁兼容设计具有一定的参考价值。

苏公网安备32050802011615号

苏公网安备32050802011615号