Spice 仿真以及ESD 测试结果

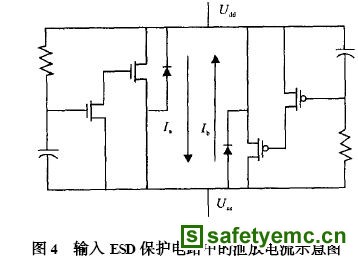

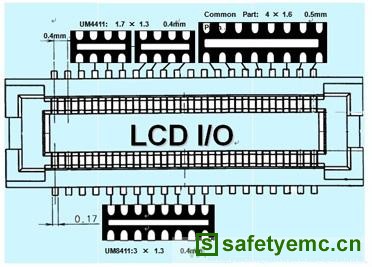

由于ESD 保护电路以及封装所带来的寄生电容和寄生电感对原有输出信号会有影响,尤其是在高速模拟电路中,频率越高信号畸变越严重,所以建立合适的仿真模型并进行有效的仿真是必须的。信号一般经过驱动, ESD 保护,和封装引线才能传到芯片外的负载上,封装的模型根据选用的封装形式和厂家提供的参数决定。 一般IC 封装会给出端口的寄生电容,电阻和电感,其等效模型如图5所示。 将该模型与前面的ESD 保护电路(图3) 串连起来就可以得到端口模型, 可用spice 对用于USB2.0 的环境,在480 MHz 频率下的收发电路进行仿真,其仿真波形如图6 所示。 输出端口out1 是不考虑端口模型的影响,480 MHz 时钟的输出较为理想,out2 是加入端口模型后的时钟输出,波形有所畸变,但仍能满足电路设计要求。

上述ESD 保护电路(见图3) 在被应用于设计USB2. 0 接口芯片中。 该芯片的最高时钟频率为480 MHz ,采用TSMC 公司的0. 25μm 混合信号工艺进行了流片。 流片后的芯片用抗静电测试仪( Thermo Keytek 公司,型号: ZAPMASTER 714)进行了测试,其结果如表1 所示,给出了在上述4 种不同的放电模式下的耐压值。 测试结果表明在所有测试条件下的人体模型最高击穿电压(V) 超过了正负2 500 V。

结 论

在高速的模拟电路设计中, ESD 成为芯片能否正常工作的重要考虑因素。 文中提出了在用栅极接地的NMOS 和栅极接电源PMOS 管的基础上,结合电源与地之间的高速静电泻放回路的新的电路结构。 经过实际测试,在HBM 模型下可以承受正负2 500 V 的高压,并且该电路对正常信号的影响。

苏公网安备32050802011615号

苏公网安备32050802011615号