新的保护方法

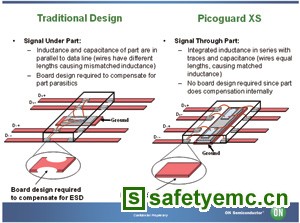

安森美半导体开发出的PicoGuard XS架构可以维持高速数据接口的信号完整性,同时提供更强的ESD保护。这种架构向上布线并穿过封装,而不是位于封装下面,借此消除走线寄生参数。这种方法将电感与ESD二极管集成在一起以匹配信号线路阻抗,从而摒弃任何类型的外部补偿。集成电感降低钳位电压及受保护ASIC所流入的残余电流,从而改善ESD性能。

图1 PicoGuard XS与传统ESD保护设计比较

这种架构也省却了扼流圈的需要或PCB上的走线宽度修改。而且,这种架构与电路板堆叠无关,使系统设计人员能够使用多个电路板供应商的产品,无须为各个供应商的产品进行定制阻抗匹配。这种架构能够提供与所涉及PCB层数、介电厚度及其他布线方面变量无关的匹配阻抗。

新方法的技术原理

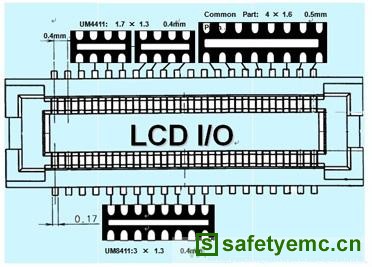

图2显示了标准ESD保护元件的特征图。电感元件表示的是源自邦定线和连接至保护元件的PCB走线的寄生电感。在这种标准元件模型中,电感元件为抵御高转换率(slew rate)ESD冲击的高阻抗,限制了保护元件快速吸收ESD能量的能力,使得更多的能量进入受保护的ASIC。

图2 传统ESD器件表征

图3 PicoGuard XS器件表征

作为对比,PicoGuard XS架构的电感元件与连接至受保护ASIC的导电通道串联,如图3所示。这元件实际限制冲击受保护器件的电流和电压。首先,ESD冲击会出现的连接器端的电感元件L1存在电抗,这电抗的方向与ESD电流方向相反,帮助限制峰值冲击电压。然后,ASIC端的电感元件L2的电抗迫使更有限的ESD冲击电流通过ESD保护元件分流。与此同时,这两个串联元件的电压降也发挥作用,降低受保护ASIC遭受的钳位电压。

苏公网安备32050802011615号

苏公网安备32050802011615号