抑制辐射骚扰的最好方法还是重新对PCB的设计进行修正并重新合理设计,但在我们在实际工作中也经常发现,如用户在摩尔实验室(MORLAB)进行测试并发现辐射骚扰不合格时, 此时的产品往往已经设计定型并处于等待上市的最后阶段,重新修改PCB的设计工作,不仅会增大生产成本,而且会使得产品延误而错失商机。因此研究产品辐射骚扰的抑制在具有一定的现实意义。

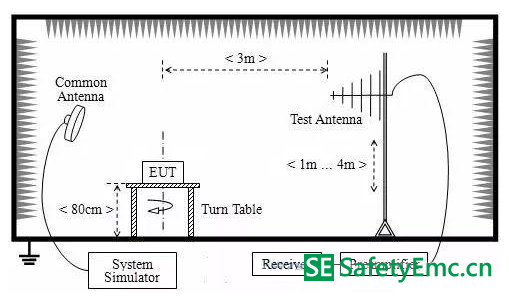

RE测试场地布局如下:

辐射骚扰测试限值要求

根据不同的产品所对应的标准具体要求也会有所差别,但大体可归纳如下:

辐射骚扰整改的一般步骤

1. 要了解产品的工作特点,尽量多地了解当前产品辐射骚扰超标具体情况;

2. 针对具体失败问题,了解产品电路设计原理,根据客户提供的信息判断何种类型的超标。找出骚扰源,工作所需的振荡信号;

3. 分析电路,使用近场探头进行探查以确定骚扰源和其的的骚扰途径;

4. 为了确保方法正确,采取必要的排查测试并做问题症结的进一步确认;

5. 综合分析结果,找到造成骚扰的根本原因,这时就可采取措施进行整改了。根据超标的严重性一般可采用源头整改或为了方便直接从骚扰途径处下手(可以以6dB为限);

6. 验证整改效果,效果不理想则返回继续分析查找原因更改整改方法,效果好则要求更便捷经济理想的方法;

7. 总结经验,记录整改方法;

如何查找辐射杂散骚扰产生的原因

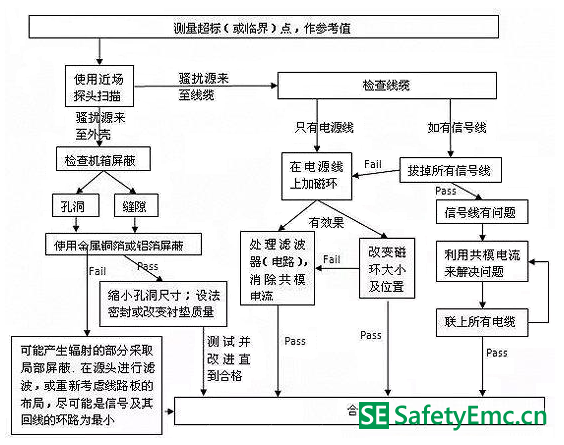

一般来讲,大多数情况下都是可以通过排除法来查找辐射产生的原因(尤其是对设备不是很了解的情况)。具体分析过程如下表流程所示:

苏公网安备32050802011615号

苏公网安备32050802011615号