整合型相位噪声之测量与相位抖动之计算

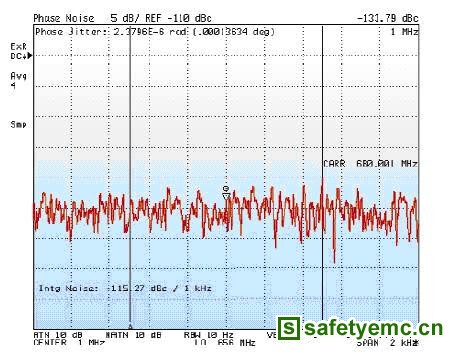

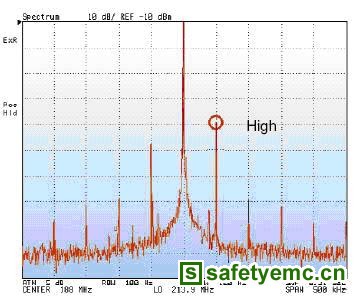

在特定的频率范围内,VCO/PLL讯号测试系统能在相同的屏幕上,显示出相位噪声和整合型相位噪声之功率,以做为改进开发和提升设计效率的参考。图十是一个测量整合型相位噪声的实例。相位噪声功率之总和〔dBc〕,在光标指定的偏移频率范围内(1kHz)之测量结果,显示在屏幕的左下角。

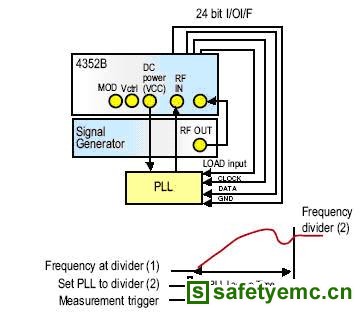

图六:射频频率和DC控制电压的量测

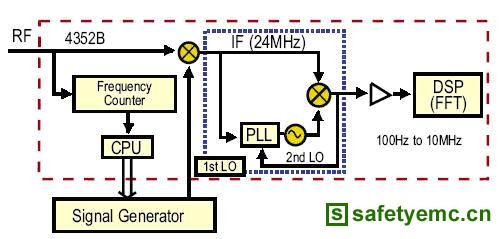

图七:载波 锁定多模块PLL电路

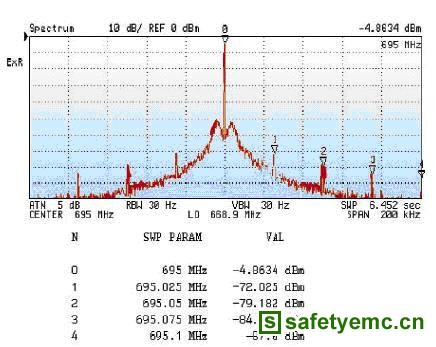

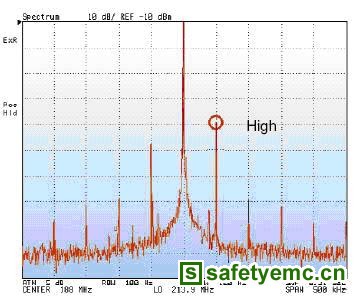

图八:VCO相位噪声的测量实例

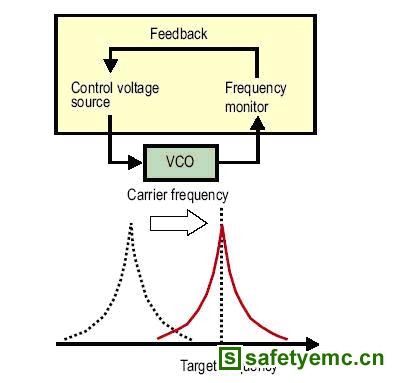

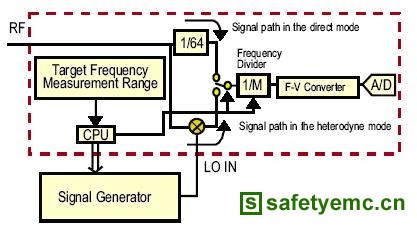

图九:自动化频率控制

图十:整合型相位噪声功率之测量实例

锁相回路的特性参数

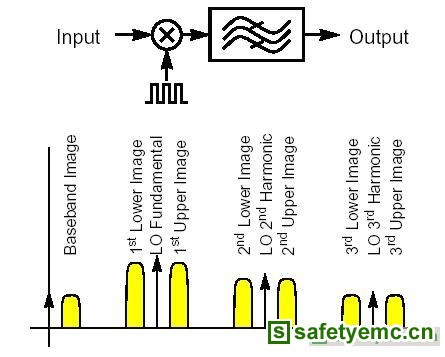

锁定时间和PLL频率合成器的寄生响应(spurious response),彼此是互为取舍(trade-off)的关系。一个PLL频率合成器一般是由许多组件构成的,因此必须考虑到每一个组件参数的可能变化量,以确保制程的质量。当设计一个优化的回路滤波器时,在PLL的原型设计时间,下列参数必须纳入评估:

1) 频率〔Hz〕

2) 射频功率〔dBm〕

3) 相位噪声〔dBc/Hz〕

4) 参考源漏泄(寄生频率特性)〔dBc〕

5) 锁定时间〔sec〕

6) 回路带宽

对PLL频率合成器做性能评估,通常需要各种不同的测量仪器,包括如下:

1) 用来测量锁定时间的调变域分析仪

2) 相位噪声测量系统

3) 评估寄生频率特性的频谱分析仪

4) PLL控制器

每次连接结束之后,必须对测量系统做性能校验,这对重复测量是必需的。当回路滤波器的特性或振荡频率改变时,测量用的组态设定也必须重新改变,而这种冗长的工作会延长产品的开发时间。因为PLL频率合成器是被设定在期望的频率上,当利用数字方式控制PLL芯片时,则一个PLL控制电路或一个PLL控制程序是不可或缺的。因此,除非直到控制电路或控制程序完全启动,否则不可能执行频率合成器的测量。因为当PLL频率一变动时,测量系统很难和它同步,PLL锁定时间就很难被精准地测得。

时间和频率的分辨率

PLL锁定时间的测量与瞬间频率分析,传统上是使用一台调变域分析仪来执行。在这种情况下,频率的分辨率(resolution)是由取样间隔和测量频率来决定的。

锁相回路的特性评估

除了VCO测量功能,VCO/PLL讯号测试系统也能控制PLL频率合成器。在不改变连接的情况下, 高速相位噪声测量和频谱测量都能被执行(如图十一)。快速的相位噪声测量功能可以大幅降低评量的时间,因此就能改进回路滤波器的设计效率。

图十一:PLL寄生频率的测量实例

利用程控PLL

VCO/PLL讯号测试系统,能够让用户设定希望的除频比率(frequency division ratio),利用程序(例如:IBASIC)与24-位数字式I/O通讯端口,来测量锁定时间,并与PLL合成器的频率变动同步。这不需外接的个人计算机支持(如图十二)。

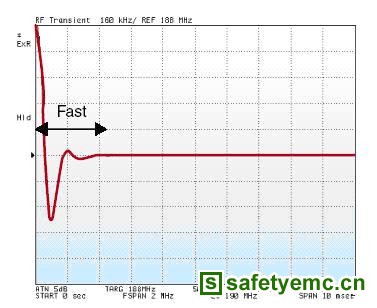

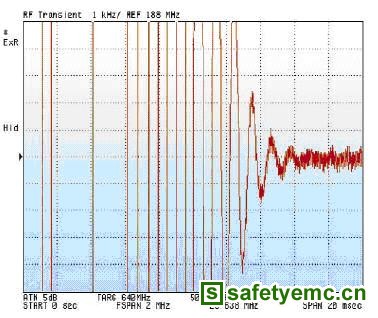

频率的瞬间测量

图十三显示VCO/PLL讯号测试系统的瞬间频率测量。此系统使用一个鉴频器(frequency discriminator)将频率转换成电压,在全部的频率测量范围内,这可使瞬间频率测量具有12.5微秒(ms)的分辨率,以及50 Hz的频率分辨率(如图十四所示)。

图十二:PLL芯片控制和锁定时间之测量

图十三:瞬间频率的测量方法

寄生频率与锁定时间的测量

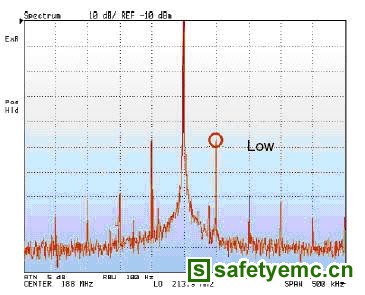

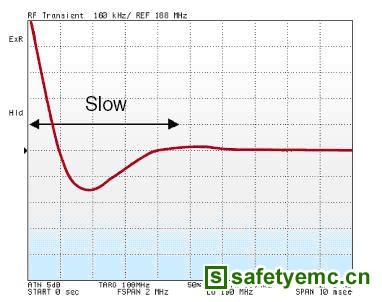

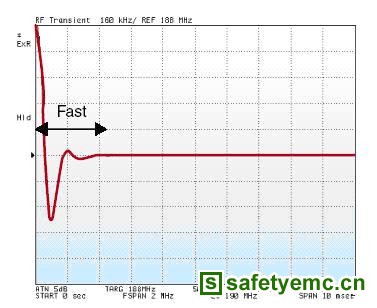

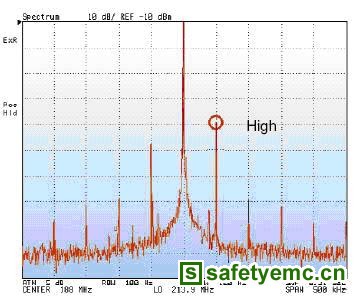

一般而言,在整个合成振荡器的开发过程中,回路滤波器的设计是最有决定性的一环。由于回路滤波器是在相位比较器(phase comparator)和VCO控制电压输入端之间的低通滤波器(low-pass filter),它可以消除由相位比较器所产生的相位修正脉冲(phase correction pulse)里的高频讯号(high frequency component),因此只有直流讯号(DC component)提供给VCO使用。通常,若回路滤波器的截止频率越低,由相位比较器产生的参考源漏泄就越能被抑制。因此,PLL寄生频率也会被抑制,如图十五所示。此外,一个截止频率较低的回路滤波器,在接近中心频率的偏移范围内,是不会抑制相位噪声的,这是因为封闭回路的负回馈区域被窄化了。这使得PLL的响应变慢(如图十六),并使频率切换的设定时间(PLL锁定时间)增长。相反的,若截止频率较高,可加速PLL的响应和缩短PLL的锁定时间,如图十七所示。当接近载波频率时,相位噪声会被抑制,但参考源漏泄却无法被抑制。

由此可知,PLL输出讯号是调频(FM)的,并且包含高尖峰值(如图十八)。当设计回路滤波器时,必需考虑到相位噪声、寄生频率、PLL锁定时间的取舍、回路滤波器的频率特性、以及一些「设计的边际效益(design margin)」,因为两个以上的VCO即使使用相同的规格来设计PLL,它们也将会有些许不同的特性产生。寄生频率的高低、相位噪声与瞬间频率的评估,在各种情况之下,将决定PLL回路设计的成败。「设计的边际效益」不一定是指回路滤波器的最大输出,而是指在不会耗尽或耗损回路滤波器的前提下,回路滤波器所产生的输出,这是一个最佳的状态。

图十四:瞬间频率的测量实例

图十五:在较低的截止频率下之寄生特性

图十六:在较低的截止频率下之锁定时间特性

图十七:在较高的截止频率下之锁定时间特性

频率合成振荡器的设计

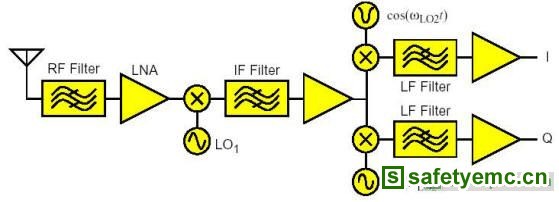

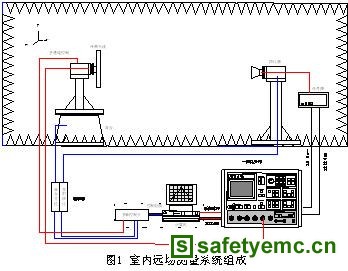

PLL频率合成振荡器必须能够产生稳定的高频输出讯号。如图一所示,由石英芯片产生的参考频率和从VCO回馈的频率,在PLL芯片里的相位比较器中做比较。当两者的频率和相位不同时,PLL就会自动控制VCO,改变其输出的频率特性,使两者的频率和相位恢复一致。石英芯片产生的参考高频是很稳定的,而且经过除频(分频)器之后,相位比较器是将两个相当低的频率做比较的,因此VCO输出的高频讯号能够很稳定。如之前所说的,改变VCO的输出频率是藉由改变除频器的除频比率(dividing percentage),它可以利用一个PLL控制电路或一个PLL控制程序达成。例如:若VCO的输出频率为134MHz,从收发机传来的射频讯号之频率是150MHz,经过下行转换器(down-converter)之后,将降为16MHz的中频。此时,PLL必须透过回路滤波器提供稳定的134MHz频率给VCO。

设计除频器之前,必须先拟定数据格式(data form)。例如:选定两个字节(2-byte)当成数据格式,其中第一个位是被当成控制位(control bit),1代表参考频率,0代表回馈(比较)频率。如下所示:

虽然,参考频率或回馈频率的除频器都可使用上述的数据格式来决定除频比率,但是两者的处理方法是不同的。参考频率的除频器将16位的数据,当成一个区块来处理,除数的大小范围是从5到65,535。回馈频率的除频器将16位的数据,区分成两个区块来处理,分别是20~25和26~215。此除频器里的「回收计数器(swallow counter)」处理20~25,「可编程计数器(programmable counter)」则处理26-215。两种计数器的大小范围,前者是0~63,后者是5~1023,所以此除频器的除数大小范围是320~ 65535,如下所示:

VCO电路的设计

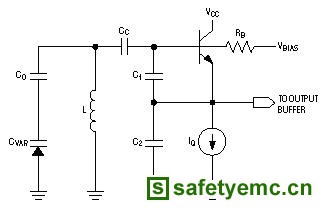

如图十九所示,它是使用Colpitts LC振荡电路。虽然目前有许多振荡器电路可以被用来设计射频VCO,但是其中最有效益的就是Colpitts的共集级(common-collector)电路。此电路适用的频率范围很广,可以从射频到中频,它是由低价位的电感和变容二极管(varactor diode)组成,如图十九所示。这是一个并联谐振电路,电感或电容上的任何变动都会改变振荡频率。在并联模式下,允许我们能够直接对振荡器做分析。就电路特性而言,它是一种具有正回馈功能的LC放大器。在图十九中,若忽略寄生因素,CC>>C1和C2,C1>Cπ(Cπ是基级-射级之间的电容),经计算可以求得振荡频率f0为:

CO 是变容二极管的耦合电容值,CVAR是变容二极管的电容值,CT是总电容值。

集级电压是分配给C1和C2,并在射级接地。当施予负电压时,CVAR会变小,所以可以藉此调整振荡频率的大小。如果再详细研究和计算,甚至可以求得回路增益、振荡振幅、相位杂音,正如前面介绍的VCO/PLL讯号测试系统的部份功能。

图十八:在较高的截止频率下之寄生特性

图十九:VCO的设计实例

结语

其实,射频或微波电路设计已经有百年的历史了。如今因为集成电路制程的进步和无线应用的开放与流行,突显了射频电路的重要性。设计射频电路首重基本观念、专有名词、技术规格的充分了解,唯有不断的学习、研究和实作,经年累月之后,才会有启发和成果,这是无法投机取巧的。本文所介绍的VCO/PLL测量和设计技术,包含许多设计原理和实作细节,在进行射频电路开发时,必须充份考虑,才能事半功倍。

苏公网安备32050802011615号

苏公网安备32050802011615号