18、电容跨接两个不同的电源铜箔分区用作高频信号的回流路径,众所周知电容隔直流通交流,频率越高电流越流畅,我的疑惑是现今接入PCB中的电平大都是经过虑除交流的,那么如前所述电容通过的是什么呢?"交流的信号"吗?

答1:这个问题很有点玄妙,没见过很服人的解释。对于交流,理想的是,电源和地“短路”,然而实际上其间的阻抗不可能真的是 0 欧。你说的电容,容量不能太大,以体现出“低频一点接地,搞频多点接地”这一原则。这大概就是该电容的存在价值。经常遇到这样的情况:2个各自带有电源的部件连接后,产生了莫名其妙的干扰,用个瓷片电容跨在2个电源间,干扰就没了。

答2:该电容是用来做稳压和EMI用的,通过的是交流信号。“现今接入PCB中的电平大都是经过虑除交流的”的确如此,不过别忘了,数字电路本身就会产生交流信号而对电源造成干扰,当大量的开关管同时作用时,对电源造成的波动是非常大的。不过在实际中,这种电容主要是起到辅助的作用,用来提高系统的性能,其它地方设计的好的话,完全可以不要。

答3:交流即是变化的。对于所谓的直流电平,比如电源来说,由于布线存在阻抗,当他的负载发生变化,对电源的需求就会变化,或大或小。这种情况下,“串联”的布线阻抗就会产生或大或小的压降。于是,直流电源上就有了交流的信号。这个信号的频率与负责变化的频率有关。电容的作用在于,就近存储一定的电荷能量,让这种变化所需要的能量可以直接从电容处获得。近似地,电容(这时可以看成电源啦)和负。

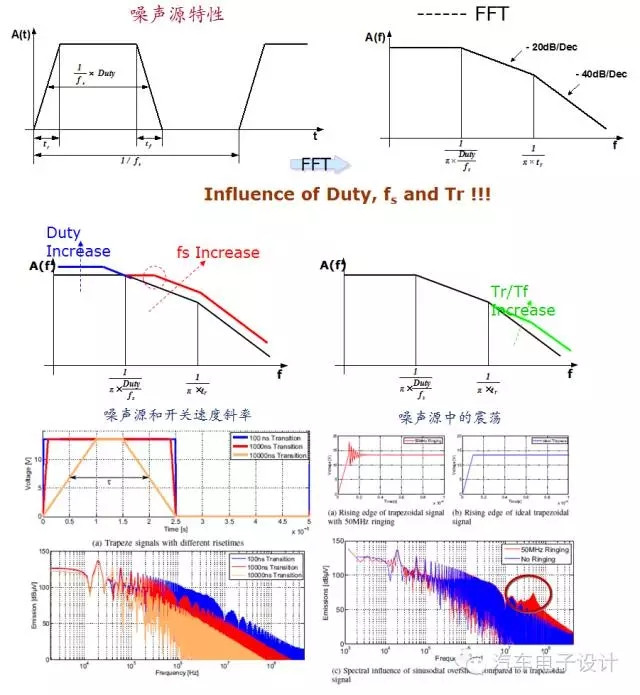

19、公司新做了一款手机,在做3C认证时有一项辐射指标没过,频率为50-60M,超过了5dB,应该是充电器引起的,就加了几个电容,其它的没有,电容有1uF,100uF的。请问有没有什么好的解决方案(不改充电器只更改手机电路)。在手机板的充电器的输入端加电容能解决吗?

答1:电容大的加大,小的改小,串个BIT,不过是电池导致的可能性不是很大。

答2:你将变频电感的外壳进行对地短接和屏蔽试试。

20、PCB设计如何避免高频干扰?

答:避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces在模拟信号旁边。还要注意数字地对模拟地的噪声干扰。

21、PCB设计中如何解决高速布线与EMI的冲突?

答:因EMI所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。 所以, 最好先用安排走线和PCB叠层的技巧来解决或减少EMI的问题, 如高速信号走内层。 最后才用电阻电容或ferrite bead的方式, 以降低对信号的伤害。

22、若干PCB组成系统,各板之间的地线应如何连接?

答:各个PCB板子相互连接之间的信号或电源在动作时,例如A板子有电源或信号送到B板子,一定会有等量的电流从地层流回到A板子 (此为Kirchoff current law)。这地层上的电流会找阻抗最小的地方流回去。所以,在各个不管是电源或信号相互连接的接口处,分配给地层的管脚数不能太少,以降低阻抗,这样可以降低地层上的噪声。另外,也可以分析整个电流环路,尤其是电流较大的部分,调整地层或地线的接法,来控制电流的走法(例如,在某处制造低阻抗,让大部分的电流从这个地方走),降低对其它较敏感信号的影响。

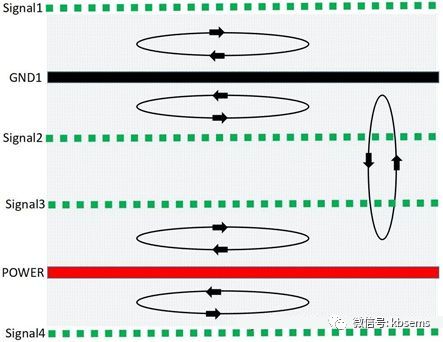

23、PCB设计中差分信号线中间可否加地线?

答:差分信号中间一般是不能加地线。因为差分信号的应用原理最重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如flux cancellation,抗噪声(noise immunity)能力等。若在中间加地线,便会破坏耦合效应。

24、适当选择PCB与外壳接地的点的原则是什么?

答:选择PCB与外壳接地点选择的原则是利用chassis ground提供低阻抗的路径给回流电流(returning current)及控制此回流电流的路径。例如,通常在高频器件或时钟产生器附近可以借固定用的螺丝将PCB的地层与chassis ground做连接,以尽量缩小整个电流回路面积,也就减少电磁辐射。

25、在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请介绍在高速(>100MHz)高密度PCB设计中的技巧?

答:在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

1).控制走线特性阻抗的连续与匹配。

2).走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。

3).选择适当的端接方式。

4).避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5).利用盲埋孔(blind/buried via)来增加走线面积。但是PCB板的制作成本会增加。 在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

26、PCB设计中模拟电源处的滤波经常是用LC电路。但是为什么有时LC比RC滤波效果差?

答: LC与RC滤波效果的比较必须考虑所要滤掉的频带与电感值的选择是否恰当。 因为电感的感抗(reactance)大小与电感值和频率有关。如果电源的噪声频率较低,而电感值又不够大,这时滤波效果可能不如RC。但是,使用RC滤波要付出的代价是电阻本身会耗能,效率较差,且要注意所选电阻能承受的功率。

27、PCB设计中滤波时选用电感,电容值的方法是什么?

答:电感值的选用除了考虑所想滤掉的噪声频率外,还要考虑瞬时电流的反应能力。如果LC的输出端会有机会需要瞬间输出大电流,则电感值太大会阻碍此大电流流经此电感的速度,增加纹波噪声(ripple noise)。 电容值则和所能容忍的纹波噪声规范值的大小有关。纹波噪声值要求越小,电容值会较大。而电容的ESR/ESL也会有影响。 另外,如果这LC是放在开关式电源(switching regulation power)的输出端时,还要注意此LC所产生的极点零点(pole/zero)对负反馈控制(negative feedback control)回路稳定度的影响。

苏公网安备32050802011615号

苏公网安备32050802011615号