2.2 晶振时钟电路及频率

2.2.1 时钟电路的设计及参数计算

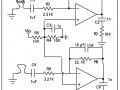

晶振采用并联谐振的工作方式,如图1中23~24脚外围电路所示。电路总的相移为360°,其中反向器提供180°的相移,R7和C22提供90°的滞后相位,晶振和电容C1也带来90°的相位滞后。并联工作的晶振是作为电感用的。晶振接入电容补偿相移以满足振荡条件。

偏振电阻R1用于设置反相器的偏置点,典型值是Vcc引脚值的二分之一。R1过小,将降低环路增益,破坏网络反馈条件,典型值是1~5 MΩ。可以观察23引脚的输出频率随电压的变化情况。如果晶振有过驱动,则增大电压后,输出频率会下降,此时应该微调电阻R2(调高)。注意,R2应该足够小,以确保振荡器在小于最小工作电压的情况下能够起振。C1和晶振的旁路电容Co及反相器的输入电容共同构成了晶振的输入电容。要提供稳定度,晶振的输入电容典型值可选择20~30 pF。

2.2.2 频率的选择

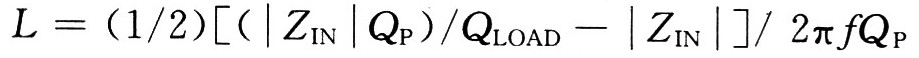

根据抽样定理可知,时钟频率fref(fref/2即为Na-quist频率)对量化噪声功率、冗余信号电平以及输出频谱中由于不满足抽样定理而带来的干扰信号、时钟频率和鉴相器的参考基准频率fo_DSS(即由DSS得到的信号频率fref/fo_DSS)的比率越大,频率合成器的输出信号频谱所受到的干扰就越少。时钟频率的具体计算方法如下:

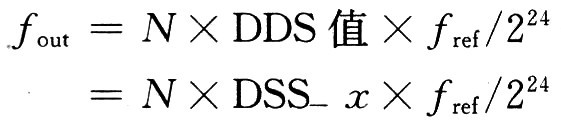

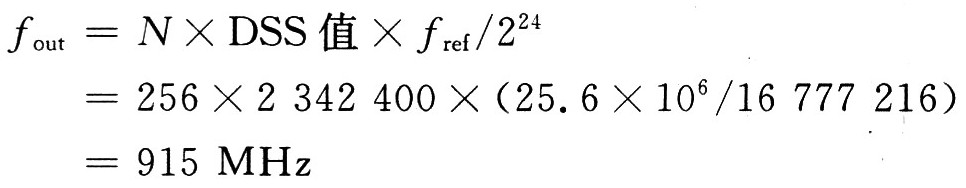

假设要使基于DDS的PLL构成的频率合成器的输出频率为906.24 MHz(与DSS得到的输出信号频率fo_DSS即鉴相器的参考基准频率要区别开来),经过256或者512分频(可选),假设为256,那么DDS的输出信号频率fo_DSS就应等于906.24/256=3.54 MHz,可得到PLL的输出频率的计算公式:

式中:预标值N可选择256或者512,DDS_x为控制字A或B的值。

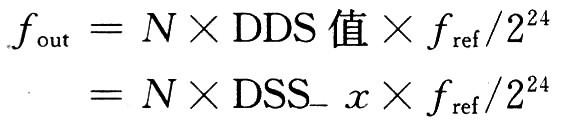

DSS频率值可通过串行口控制字编程设置,其最低有效位是2°,最高有效位是223。两个最高位(23,22位)用户不可访问,系统内部自动置为0,21-0位,并由用户编程设置。其中,A字对应DDS-O即模式0的频率;B字对应DDS-1即模式1的频率;C字控制PLL、数据限制器和模式1寄存器的设置;D字控制调制方式(如频偏大小)和模式O寄存器的设置。

2.3 载波频率计算

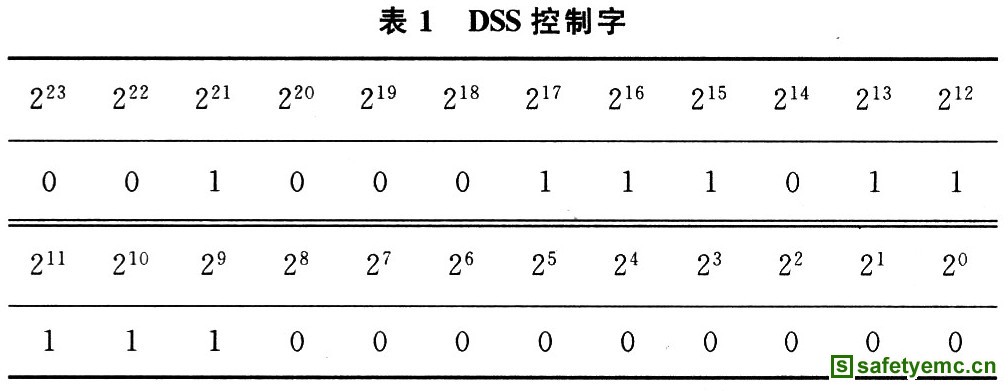

由时钟频率经过基于DDS的频率合成器可得到VCO输出的载波频率。对于典型的25.6 MHz时钟频率,由表1可得当DDS控制字为001,000,111,0000,000,000时,可计算出的VCO输出频率即载波频率为915 MHz。

由表1可知:

最后的VCO输出频率为:

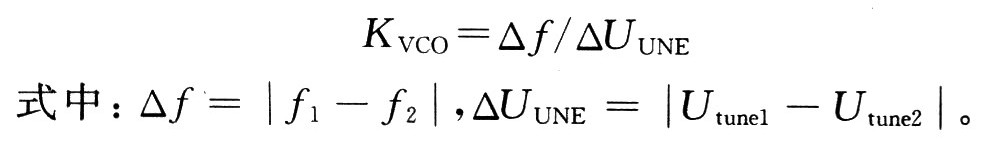

2.4 DSS控制字的计算

TRF6900的FSK调制是由专门的FSK频偏寄存器来完成。A,B控制字用来设置接收机和发射机的频率及信道。在应用系统的使用中,A,B控制字用来设置FSK频偏。用于FSK方式时DDS控制字的计算方法如下:

假设载波频率为915.O MHz,频偏为20 kHz,即A字对应的VCO输出频率fout1=915.00 MHz;B字对应的VCO输出频率fout2=915.02 MHz;时钟频率fclock=fref=25.6 MHz;分频比N=256。下面计算A,B控制字:

A字对应于DDS_O值:

所得的二进制的DDS_O将装入A控制字中。

B字对应于DDS_1值:

所得的二进制的DDS_1将装入B控制字中。

苏公网安备32050802011615号

苏公网安备32050802011615号