对于第一条,通常通过布局走线就能够略知一二,高dv/dt的器件和线路集中在原边开关管和变压器,最典型的情况是原边开关管或者变压器靠近输入L/N线,这种情况造成的问题只能通过减小耦合电容来解决,拉远动点和输入线的距离,采用电场屏蔽措施。实际应用中最常见的方法是将输入电解电容(外壳接原边地)或接原边静点的散热片置于原边开关管和输入L/N之间,将变压器的磁芯接原边静点(磁芯为原边的情况)。

另一个反面的案例是绝大多数灌胶的应用中,由于胶的介电常数通常为空气的数倍,灌胶后的共模传导会全面恶化。

第二条和第一条情况有相似之处,只是耦合回路是大地而不是输入L/N线,因此第二条干扰源通常有比较大的面积,比如插件TO220的MOSFET(散热器为漏极动点)、悬浮的变压器磁芯以及动点的大面积铺铜(对于依赖漏极散热的硅MOS,大面积铺铜需要特别注意)。在实际应用中,同一个措施可能对对第一条和第二条同时有效,例如原边MOSFET增加接静点的散热器,变压器磁芯接原边静点等。

第三条情况相对复杂的一条,也是工程应用中大有可为的一条。

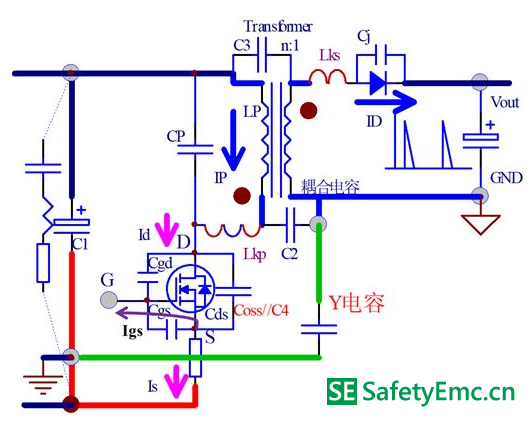

3)开关动点高的dv/dt通过变压器耦合到副边,进而从副边输出耦合到地平面(或者从原边耦合到地平面)

下面重点分析第三条的机理和解决措施。

上用不同颜色示意出了变压器原边动点对副边静点的等效电容Cps,副边动点对原边静点的等效电容Csp,原副边跨接电容Cy以及副边对大地的寄生电容Ce(原边对大地的寄生电容没有画出来),同时示意出了流过这些电容上的电流。

常规的输出同步整流底边工作时,从变压器相位可以看出,原副边的动点是反相位的,这意味着图中的Ips和Isp极性相反,也就是说流过变压器的原副边电流是叠加的,这个叠加后的电流一部分通过Y电容在原副边形成环路,另一部分则通过寄生电容流向了大地,这部分流向大地的高频电流也就是传导共模来源之一,大多数情况下是主要贡献者。

那么,为了减小共模电流Ie,很显然有两个途径:一是减小变压器原副边共模电流,二是增大跨接Y电容,减小寄生电容的分流。

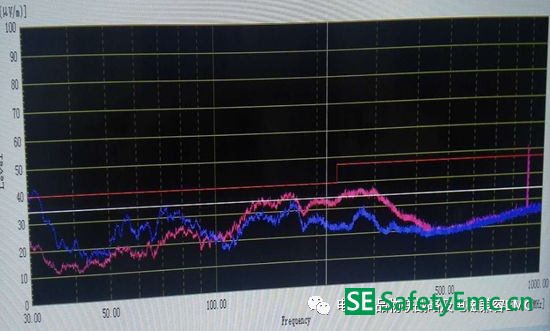

第二条途径想必是大多数工程师曾亲测有效的,有效频段甚至是整个CE测试频段和RE测试低频段。第一条途径说白了就是要整改变压器了,整改的手段可能很多工程师都用过,只是没有和机理一一对应。

苏公网安备32050802011615号

苏公网安备32050802011615号