摘要:在现代高速数字电路设计中,信号完整性和电磁兼容性是设计中非常重要的问题。只有很好地控制串扰、地弹、振铃、阻抗匹配、退耦等电磁兼容因素,才能设计出成功的电路。模拟电路原理在高速数字电路设计的分析和应用中发挥着很大的作用。本文较详细地解释了高速数字电路设计中上述电磁兼容问题的产生原因以及解决方法,最后给出了一个实际设计的仿真实例来说明以上现象。

关键词:高速数字电路;信号完整性;电磁兼容性;EDA仿真

0 引言

纵观电子行业的发展,1992年只有40%的电子系统工作在30 MHz以上,而且器件多使用DIP、PLCC等体积大、引脚少的封装形式;到1994年,已有50%的设计达到了50 MHz的频率,采用PGA、QFP、RGA等封装的器件越来越多;1996年之后,高速设计在整个电子设计领域所占的比例越来越大,100 MHz以上的系统已随处可见,采用CS(线焊芯片级BGA)、FG(线焊脚距密集化BGA)、FF(倒装芯片小间距BGA)、BF(倒装芯片BGA)、BG(标准BGA)等各种BGA封装的器件大量涌现,这些体积小、引脚数已达数百甚至上千的封装形式已越来越多地应用到各类高速、超高速电子系统中。

从IC芯片的发展及封装形式来看,芯片体积越来越小、引脚数越来越多;同时,由于近年来IC工艺的发展,使得其速度也越来越高。这就带来了一个问题,即电子设计的体积减小导致电路的布局布线密度变大,而同时信号的频率还在提高,从而使得如何处理高速信号问题成为一个设计能否成功的关键因素。随着电子系统中逻辑复杂度和时钟频率的迅速提高,信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要。对于低频设计,线迹互连和板层的影响可以不考虑,但当频率超过50 MHz时,互连关系必须考虑,而在评定系统性能时还必须考虑印刷电路板板材的电参数。因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性(Signal Integrity,SI)问题。

当硬件工作频率增高后,每一根布线网络上的传输线都可能成为发射天线,对其他电子设备产生电磁辐射或与其他设备相互干扰,从而使硬件时序逻辑产生混乱。电磁兼容性(Electromagnetic Compatibility,EMC)的标准提出了解决硬件实际布线网络可能产生的电磁辐射干扰以及本身抵抗外部电磁干扰的基本要求。

1 高速数字电路设计的几个基本概念

在高速数字电路中,由于串扰、反射、过冲、振荡、地弹、偏移等信号完整性问题,本来在低速电路中无需考虑的因素在这里就显得格外重要;另外,随着现有电气系统耦合结构越来越复杂,电磁兼容性也变成了一个不能不考虑的问题。

要解决高速电路设计的问题,首先需要真正明白高速信号的概念。高速不是就频率的高低来说的,而是由信号的边沿速度决定的,一般认为上升时间小于4倍信号传输延迟时可视为高速信号。即使在工作频率不高的系统中,也会出现信号完整性的问题。这是由于随着集成电路工艺的提高,所用器件I/O端口的信号边沿比以前更陡更快,因此在工作时钟不高的情况下也属于高速器件,随之带来了信号完整性的种种问题。

2 高速数字电路设计的基本要求

在PCB设计中,电磁兼容性的分析也离不开布线网络本身的信号完整性,主要分析实际布线网络可能产生的电磁辐射和电磁干扰,以及电路板本身抵抗外部电磁干扰的能力,并且依据设计者的要求提出布局和布线时抑制电磁辐射和干扰的规则,作为整个PCB设计过程的指导原则。电磁辐射分析主要考虑PCB板与外部接口处的电磁辐射、PCB板中电源层的电磁辐射以及大功率布线网络动态工作时对外的辐射问题。对于高速数字电路设计,尤其是总线上数字信号速率高于50 MHz时,以往采用集总参数的数学模型来分析EMC/EMI特性显得无能为力,设计者们更趋向于采用分布离散参数的数学模型做布线网络的传输线分析(TALC)。对于多块PCB板通过总线连接而成的电子系统,还必须分析不同PCB板之间的电磁兼容性能。

针对高速数字电路设计中的电磁兼容性和信号完整性问题,在进行高速PCB板设计时需要从以下一些方面进行考虑。

2.1 端接匹配

由源端与负载端阻抗不匹配导致的传输线上阻抗不连续,会引起信号线上的反射,负载将一部分电压反射回源端,造成电平的抬高,对器件产生破坏性的影响。同时,由于任何传输线上都存在固有的电感和电容,如果信号在传输线上来回反射,必然会产生振铃和环绕振荡现象,引起电路时序的失调。采用源端或终端的端接匹配是一个比较好的解决方法。

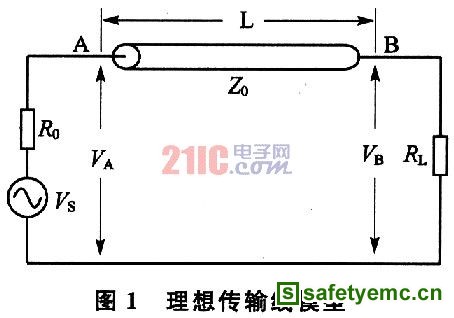

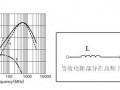

用图1所示的理想传输线模型来分析与信号反射有关的重要参数。图中,理想传输线L被内阻为R0的数字信号驱动源VS驱动,传输线的特性阻抗为Z0,负载阻抗为RL。

负载端阻抗与传输线阻抗不匹配会在负载端(B点)反射一部分信号回源端(A点),反射电压信号的幅值由负载反射系数ρL决定:

式中ρL称为负载电压反射系数,它实际上是反射电压与入射电压之比。

由式(1)可见,-1≤ρL≤+l,且当RL=Z0时,ρ1=O,这时就不会发生反射。即只要根据传输线的特性阻抗进行终端匹配,就能消除反射。从原理上说,反射波的幅度可以大到入射电压的幅度,极性可正可负。当RLZ0时,ρL>O,处于欠阻尼状态,反射波极性为正。

当从负载端反射回的电压到达源端时,又将再次反射回负载端,形成二次反射波,此时反射电压的幅值由源反射系数ρS决定:

传输线的端接通常采用两种策略:负载端并行端接匹配、源端串行端接匹配。只要负载反射系数或源反射系数二者任一为零,反射都将被消除。并行端接在信号能量反射回源端之前在负载端消除反射,即使ρ1=O,消除一次反射,这样可以减小噪声、电磁干扰(EMI)及射频干扰(RFI);串行端接则是在源端消除由负载端反射回来的信号,即使ρS=O和ρL=1(负载端不加任何匹配),只是消除二次反射,在发生电平转移时,源端信号会出现持续时间为2TD(TD为信号源端到终端的传输延迟)的半波波形,这意味着沿传输线不能加入其他信号输入端,因为在上述2TD时间内会出现不正确的逻辑态。两种端接策略各有其优缺点,不过由于并行端接的匹配网络需要与电源连接,使用较为复杂;串行端接只需要在信号源端串入一个电阻,消耗功率小而且易于实现,有较大的实际工程应用价值,所以被广泛采用。

苏公网安备32050802011615号

苏公网安备32050802011615号