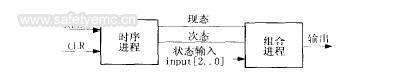

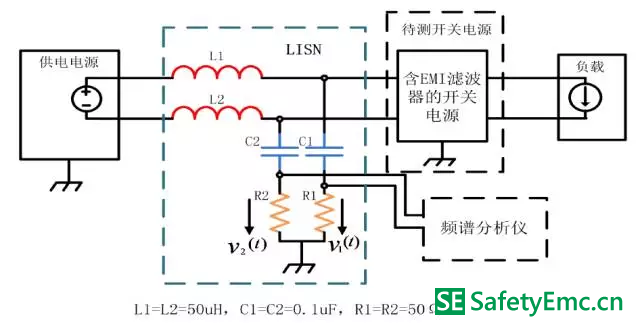

状态机的设计可采用单进程,双进程,3进程等进行编写,根据微机保护控制接口的应用特点宜采用双进程来描述状态机,即一个时序进程和一个组合进程。时序进程负责旧次态到新现态的转换,以及异步复位。组合进程完成根据现态决定状态机输出的变化,根据状态输入来决定新的次态。双进程状态机的逻辑框图如图3所示。

图3 双进程状态机逻辑图

状态机的行为及代码是一种流程控制代码,很容易用VHDL语言中的CASE语句和IF语句加以实现。时序进程与组合进程之间利用现态信号和次态信号进行同步通信。

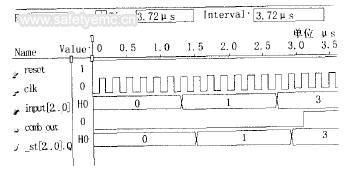

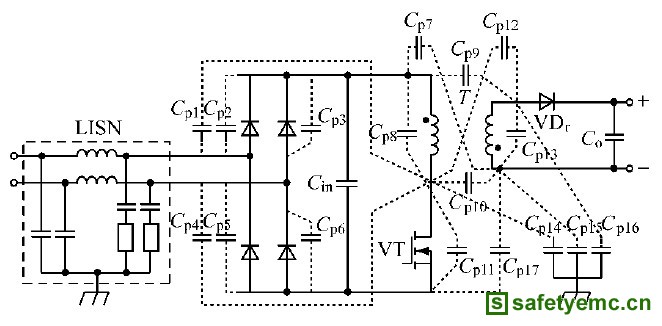

状态机仿真波形

利用Altera公司的EDA工具软件MAX+plus对用VHDL语言设计的状态机进行时序仿真,仿真波形如图4所示。

图4 状态机仿真波形

CPLD状态机抗干扰控制原理分析

基于CPU的微机系统是按指令周期顺序执行机器指令的,一旦受干扰程序出轨,则CPU不按事先编好的流程执行程序,出现死机,通常的对策是设置看门狗使CPU硬件复位,使CPU重新运行正常程序,但是从CPU死机到看门狗复位一般要经历几毫秒到1~2s,这段失控时间,继电保护控制出口的状态是不可预测的,足以对继电保护系统构成危害,严重情况就是发生误动。而基于CPLD的状态机系统,状态变换周期只有一个时钟周期,若时钟频率为5MHz,时钟周期为012Ls。若状态机受干扰进入非法状态再转入合法状态,只需2个时钟周期,即几百纳秒,不足以对状态机系统运行造成危害。可见,用CPLD状态机控制微机继电保护的控制接口,就能实现无干扰控制,获得继电保护系统的高可靠性控制。

苏公网安备32050802011615号

苏公网安备32050802011615号