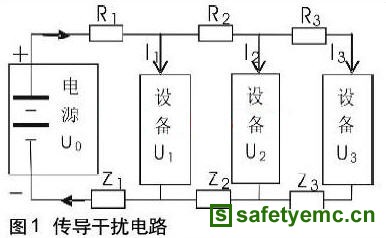

三 布线电流之去耦合分析

当IC/ASIC 有很大数量的输出驱动器时,例如说频率缓冲器、内存控制器、汇流排控制器、等等,电源电流的主要需求是要来驱动I/O 脚。因此,在I/O 布线上的电流就是很重要的,可以用来分析去耦合电容的设计。

电源接脚之电流可以使用I/O 电流以及在频率缓冲器上之『Shoot-through』电流来做预估。可以使用三角形形状的脉冲,来代表I/O 驱动器对电源电流之需求。

用此形状来预估,对某些组件已经足够了,但有时其电流波形并不是如此简单。

在图2 所示即为一非三角形状的波形。

使用信号完整性分析工具来求得I/O 布在线之电流也可以对在电源接脚上之电流脉冲做一个很好的初步预估。对于频率缓冲器,当I/O 脉冲为同步的,可以直接加总电流脉冲以求得电源接脚所需之总电流。对于内存以及总线控制器,所有的I/O 驱动器极少会在同一时间全部动作,所以使用会同时动作驱动器之平均数目来做预估会比较好。

使用之终端方式也是很重要的。例如,典型的SDRAM 内存布线只使用源端之串联电阻。对于一典型之SDRAM 内存数据线之电流,显示在图10-6 中。对比的,典型的DDR RAM 内存信号线,使用一个终端电阻连接到一个在VCC与接地电位间之电压。如图10-7 所示,驱动DDR RAM 的电流波形与SDRAM例子里的波形大大不同。

图8 及9 显示SDRAM 以及DDRAM 驱动电流之频谱。注意到此两种型式内存之谐波振幅有着非常大的差异。若是仅仅看这两种内存之电压波型,是没法发觉到其在频率频谱上有如此巨大的不同。

苏公网安备32050802011615号

苏公网安备32050802011615号