四 差模信号分析

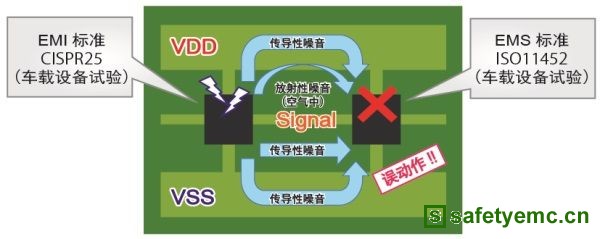

对于EMC 工程师来说,有两种的差模信号很重要:一是内部之以差模信号走线之高速线,一是外部I/O 信号之差模信号。两种在EMC 的顾虑上是不同的,但都能够以商用信号完整信分析工具来分析。

(一) 内部之差模信号线(Internal Differential Signal Lines)

在PC 板上之高速信号线使用差模布线是很常见的。然而,其并非是真正的『差模(defferential)』,只是因为这一信号线很近距离的耦合到参考平面,因而电流会在参考平面上流动。较精确的说, 这些信号是属于『complementary ,single-ended(互补的,单端)』信号。(或称之为『Pseudo-differential』虚拟差模信号)。在第五章里,讨论过不可让单端信号横越过参考平面之裂口,以免回返电流无法跨越裂口回来。通常我们会假设说,差模信号对(differential signal pair)在参考平面上之电流不会受裂口之影响。若是说差模信号的长度相同,则在布在线就不会产生共模电流。如果说布线长度不一致(或是说输出驱动端不平衡),则就会有共模电流存在于布在线。这些共模电流必须要回到其源头,所以会使用到参考平面。在参考平面上的裂口会让回返电流无法直接在线路之下方流动,就会产生如同单端线路的相同问题。

信号完整性分析工具可以用来协助分析出这些不平衡差模信号线长度之问题。以这个例子来说,我们使用IBIS 模型来分析差模驱动器以及接收器。起始的传输线长度设为10 英吋,然后将其中一条传输线长度逐步的增加。在接收器端之电流差额就是为共模电流。图10 显示,当差模布线长度之不匹配逐步增加时,其产生之共模电流之频谱。在没有不匹配状况时之电流频谱也显示为参考基线。

(在此例子中,参考基线并非为零,是因为在IBIS 模型中,输出驱动器并不是理想的平衡)。

图11 显示对比于理想匹配长度之共模电流增加量。即使是仅仅1%之不匹配,在共模电流之某些谐波频率都显示有很大的增加量。在真实产品上要做到理想之匹配是不可能的,驱动器也不尽然会是理想的匹配,因此对于差模布线应该要将其视为单端布线,所以不可以在参考平面之裂口上经过。此一讨论之重点在于使用信号完整性分析工具可以很容易的来分析布线长度不匹配之问题,并且可以提供有价值的信息给设计工程师。

(二) 外部I/O 之差模信号线

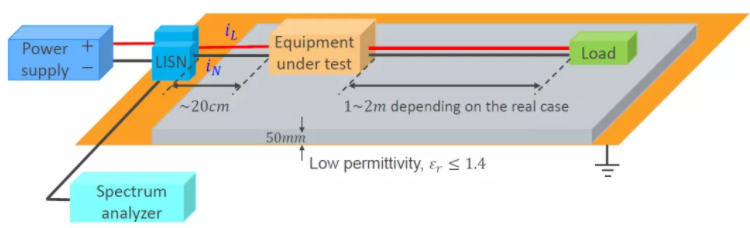

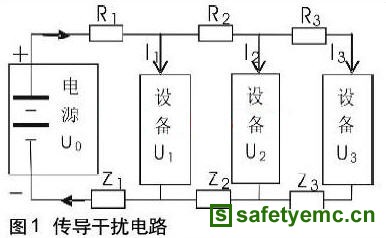

某些I/O 信号常常有用到差模信号,例如Ethernet 以及USB 数据线。信号完整性分析工具也可以用来分析这些信号线。对外部之I/O 缆线来说,在导线以及机壳间之共模电压是EMI 问题之所在。如果外部缆线对线路布线提供了一个差模负载,并且线路布线是长度匹配的,则不会有共模电压产生在缆线与机壳之间。

如前节所述,如果布线之长度不是匹配的,则在缆在线就会有共模电压产生并且跑到机壳之外。

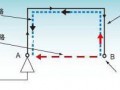

要分析此一因布线长度不匹配造成之共模电压,可以使用如图12 之电路图。

差模驱动器以外部导线阻抗作为其差模负载。在此例中,差模负载分成两半,并且这两个负载之中点,藉由一个100Ω电阻连接到接地参考点。此一假设之数值是外部缆线典型且合理之共模阻抗。当差模布线之长度为匹配时,横跨在此100Ω电阻上之共模电压为零。当长度之不匹配递增时,共模电压也会递增。图13以谐波成分来显示,当长度之不匹配增加时,此共模电压之增加量。

苏公网安备32050802011615号

苏公网安备32050802011615号