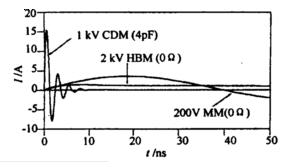

图6为2000VHBM,200VMM与1000VCDM的放电电流比较。其中,1000VCDM的放电电流在不到 1ns的时间内,便已冲到约15A的尖峰值,但其放电的总 时间约在10ns之内。所以CDM类型的静电更易造成集成电路的损伤。

图6 2000VHBM,200VMM与1000VCDM放电电流比较

2.1.4 电场感应模型 当一个器件处于静电场中,其内部将感应出电势差。此时,当某一管脚与地相碰时,器件就会对地放电。这称为电场感应模型。当将一个CMOS器件置于静电场中,其栅介质两侧就会感应出电势差。如果电势差足够大,就可能使栅氧化层击穿。这种模型的放电类似于CDM。差别仅仅在于CDM的电荷是摩擦而来,而FIM的电荷是电场感应而来。

3 静电放电(ESD)的测试

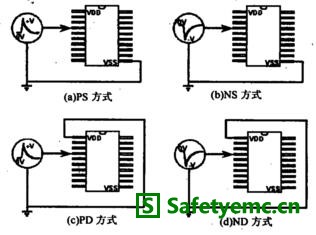

3.1.1 HBM和MM的ESD测试方式 (1)输入输出管脚对电源和地的ESD测试 由于加在输入输出端的ESD电压有正负2种可能,每一个输入输出管脚对电源和地的ESD就有4种测试方式,等效电路示意图如图7所示。

①PS方式 VSS接地,ESD正电压加到该输入输出端,对VSS放电,VDD与其他管脚悬空。

②NS方式 VSS接地,ESD负电压加到该输入输出端,对VSS放电,VDD与其他管脚悬空。

③PD方式 VDD接地,ESD正电压加到该输入输出端,对VDD放电,VSS与其他管脚悬空。

④ND方式 VDD接地,ESD负电压加在该输入输出端,对VDD放电,VSS与其他管脚悬空。

图7 输入输出管脚的静电放电测试组合

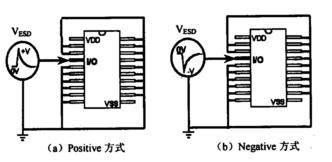

(2)管脚之间的ESD测试方式 ESD发生在无关的2个管脚之间时,静电会通过电源 线和地线从另一个管脚放电。在管脚之间的测试方式中,同样也由于ESD电压有正负两种可能而分成两种测试方式,如图8所示。

图8 管脚之间的ESD测试方式

①Positive方式 ESD正电压加在一个输入输出端,所有的其他输入输出端接地,VDD与VSS端悬空。

②Negative方式 ESD电压附加在一个输入输出端,所有的其他输入输出端接地,VDD与VSS端悬空。

(3)电源与地之间的ESD测试方式 同样,由于ESD电压的正负两种可能性,该ESD测试也有两种测试方式,等效电路示意图如图9所示。

①Positive方式:ESD正电压加在VDD端,VSS端接地,所有输入输出端悬空。

②Negative方式:ESD电压附加在VDD端,VSS端接地,所有输入输出端悬空。

图9 电源与地之间的ESD测试方式

苏公网安备32050802011615号

苏公网安备32050802011615号