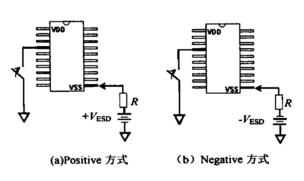

3.1.2 CDM的ESD测试 由于器件充电模型(CDM)与HBM及MM不同,因此CDM的ESD测试如图10所示。图中R为10M8以上的限流电阻,该电阻是为了防止在充电过程中造成集成电路损伤。测试过程如下: 首先,静电电压通过充电被储存到该集成电路的衬底之中,由于当今CMOS集成电路采用P和N两种衬底材料制造,对于P型衬底,VSS端与衬底相连;对于n型衬底,VDD端与衬底相连。图10中仅为P型衬底情况。当集成电路衬底充电之后,衬底就带负电压,其他管脚(包括输入输出以及VDD)再分别接地放电。

图10 器件充电模型的ESD测试方式

3.1.3 ESD的测试方法 在每一种测试方式下,集成电路的测试管脚先被加上 ESD电压,

而且在同一ESD电压下必须要加3次电压,时 间间隔约1s,加电3次之后再监测该管脚是否己被ESD 损坏,若未被损坏则提高ESD的电压,再加电3次。如此重复下去,直到该测试管脚己损坏,此时造成该测试管脚损坏的ESD测试电压称为“静电放电失效临界电压(ESD fail urethreshold)”。

3.1.4 ESD失效判断一块集成电路经过ESD测试后,通常采用以下判断方法:先把功能和电参数合格的集成电路每一个管脚进行ESD测试,再测试该集成电路的功能和电性能参数是否合格。

一般如果该电路因ESD而失效,则有以下3个失效特征:

(1)输入输出端漏电流增大。

(2)集成电路的IV特性曲线发生漂移 (3)功能失效。

4 结 语

为了避免集成电路在生产过程中被ESD损伤,通常采用ESD保护技术(包括工艺保护和电路保护)提高集成电路的ESD防护能力,然而随着CMOS工艺的发展,ESD保护技术的实现越来越困难。世界先进国家的各大IC厂商在ESD保护上的研究越来越热,各种各样的技术都被尝试用在ESD防护上,例如SCR等。

目前国内对于ESD的模型和测试方法上主要集中在人体放电模型(HBM)上,通过前面的介绍可见,机器模型和器件充电模型对器件的损伤更厉害,而且相比人体放电模型和机器模型,器件充电模型更能真实的描述器件的 ESD情形。同时,想通过器件模型和测试方式完整地测试 出器件的ESD保护能力是很复杂的。

为了避免静电对集成电路带来的损伤,除了提高器件对ESD的防护能力及进行制造环境的控制外,静电放电测试已经成为对器件可靠性评估的一个重要项目。

通过静电放电的测试一方面可以了解电路的静电放电等级,另外还可以针对ESD测试失效的器件做失效分析,以便于集成电路的设计人员改进自己的ESD保护电路,同时也帮助工艺人员在工艺上采取工艺措施提高器件的抗静电水平。

苏公网安备32050802011615号

苏公网安备32050802011615号