本文小结

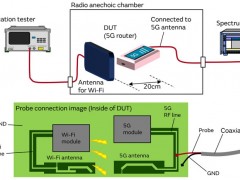

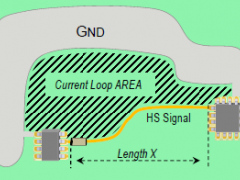

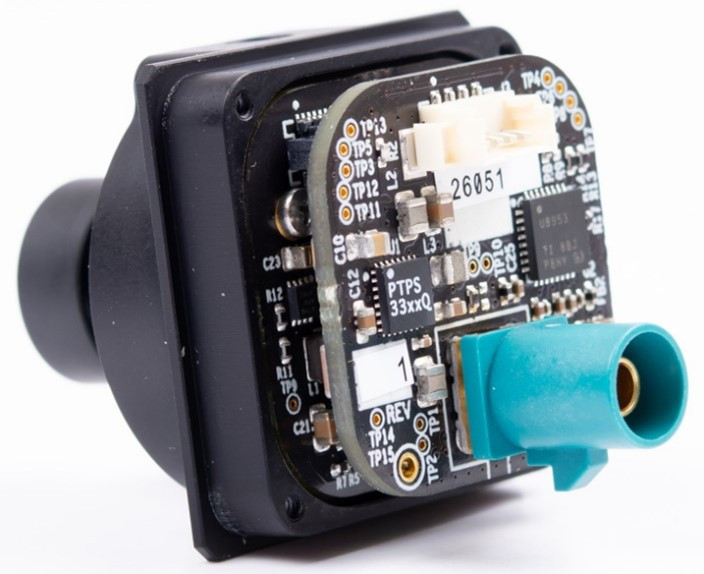

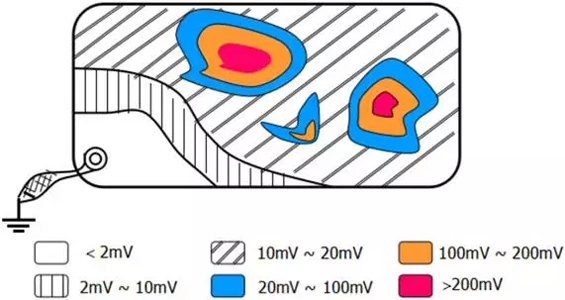

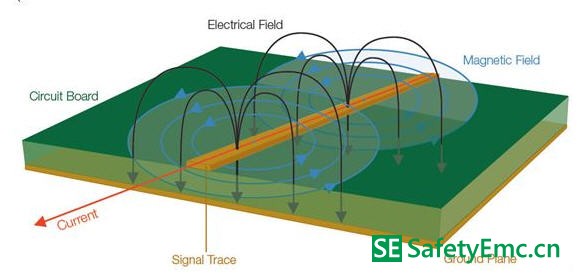

本文介绍的设计方案具有很高的控制信号转换速度,较长的通讯距离,会对高频系统产生很小的EMI。控制电路采用四层PCB和较优化的布局,还提高了抗ESD能力。在电源部分采用了DC-DC隔离和LDO器件对可编程逻辑进行分压处理。DC-DC是能量转换器件,可以对输入噪声做很好的隔离,本身产生的噪声也低于25mV,LDO器件可除稳压输出外,还可以对噪声进行抑制。采用高精度晶振和数组锁相环时钟控制可以提高系统精度和可靠性,还可以对外部时钟进行倍频处理。逻辑产生部分,采用高速CMOS器件进行缓冲并采用差分形式将信号进行转换,既提高了转换速度又增加了控制距离。由于接插件部分给传输带来的阻抗不匹配,因此接插件做接地处理,给噪声提供低阻抗返回路径,同时在接收端加匹配措施,避免了干扰信号传到下一级系统中。

高频噪声会对高频系统信号产生干扰甚至交调到高频系统中,因此对于本设计,对噪声抑制和提高EMC做了很好的改善,如晶振的电路设计中,采用0.1uF和0.001uF的π型电容网络使噪声抑制得到6dB的改善,但这种改善只有在高频部分才会有效,在低频部分和使用0.001uF的电容进行去耦效果几乎是一样的。

苏公网安备32050802011615号

苏公网安备32050802011615号