时序装置最佳化

要找出时序装置最佳的配置,可能要透过反复的试验。设计师应该了解各个区块对整体系统效能的影响。

没有一套设计配置适合于所有应用,但具有协助工具可以更明确地进行时序装置。工程师在设计装置效能所应用的基本机制包含PLL参数、回路滤波器参数、分配区段、偏移控制。此外,装置整体的噪声背景值对效能也有重大的影响。针对最佳装置的概述,可参考 Dean Banerjee(注:ISBN 0-9708207-1-2)所著的「PLL 效能、模拟、与设计,第四版」(PLL Performance, Simulation, and Design Fourth Edition)。

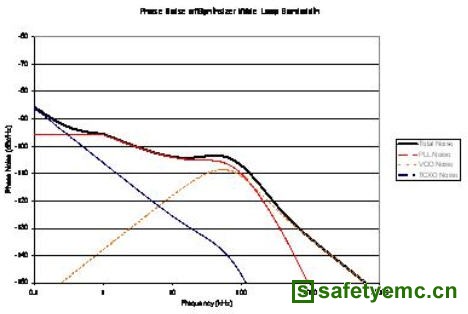

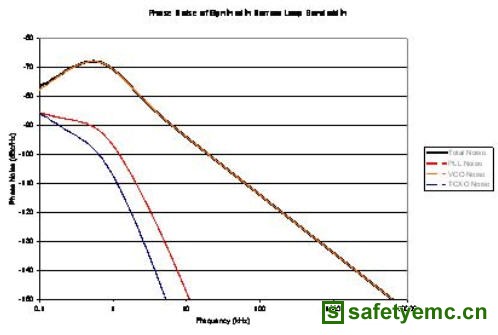

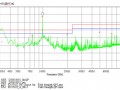

设计师可以调整特定的参数,提高效能。请参考下方描述时序装置相位噪声的图八与图九,其回路滤波器从较宽的回路频宽(如图八)调整为较窄的回路频宽(如图九所示)。

如果尚未允许该讯号拾取宽带噪声源时,参考输入(图中显示为 TCXO 曲线)一般在相位噪声中靠近其基础频率处会有非常陡的滚边。如果已拾取噪声,则可能噪声完全不会产生向下滚边。时序装置频率输出中的主要的噪声来自: 1.参考输入

2.锁相回路(PLL)

3.电压控制振荡器(VCO) 4.分配区段

5.装置噪声背景值

装置中的PLL、VCO、与噪声背景值都会有「工作分工」;而他们主要的工作包含频率平移与噪声抑制。设定回路滤波器截止频率可决定何时VCO接管PLL的噪声衰减的工作。在非常大的偏移下的相位噪声值大部分由装置噪声背景值决定,一小部份由VCO决定。

在使用窄回路频宽设计配置下,如图九所示,VCO倾向主导总噪声效能。如果PLL在靠近载波处有优异的效能,则回路滤波器应该调整为远离载波,这样它可以在参考输入中过滤任何噪声。这是一个良好的配置,特别是如果VCO在很远的(可能是 > 50 kHz)偏移下具有优异的相位噪声效能。

图八 具有宽的回路频宽之时序装置的相位噪声

图 九 具有窄的回路频宽之时序装置的相位噪声

结论

高效能数据转换器中,反复的试验可决定频率时序装置配置的优劣。设计师如果对ADC 讯号与噪声效能相关的问题具有相当的了解,并参考良好的协助设计工具,就可以达成完美的设计。表面上看来,在数据转换器设计中附属部分花时间进行最佳化看似琐碎,但此举能令消费者感受到完美设计所带来「高分辨率」的差异。

作者简介:Nicholas Gray 任职于美国国家半导体公司数据转换系统部应用工程师,电子邮件:nicholas.gray@nsc.com

苏公网安备32050802011615号

苏公网安备32050802011615号