对策改善

根据以上的分析确定以下改善对策:

1. 从板级进行改善, 降低主板上的电磁辐射。

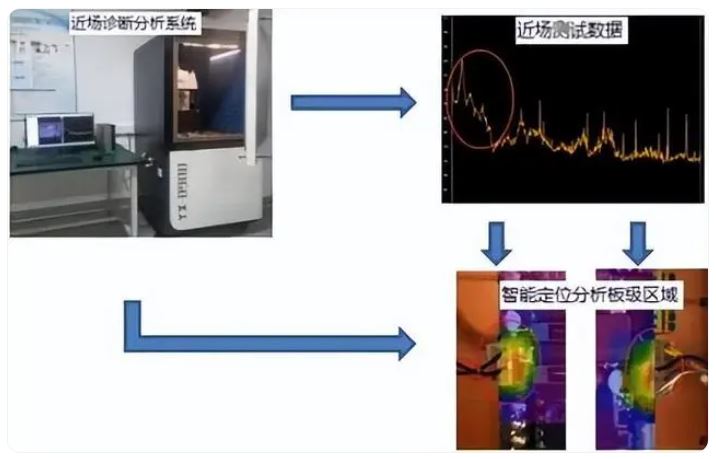

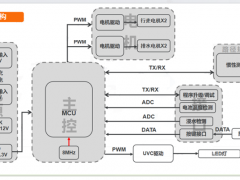

主板分析:使用 ES-67 诊断分析仪进行板级的近场测试分析,

首先,用设备的近场探头定位到主板各个区域,进行主板全方位近场扫描,数据显示 30MHz~60MHz 频率段较高;

然后,通过 ES-67 的智能分析软件,诊断定位这个频率段的主板区域位置,以下智能分析的图形显示,问题的根源在电源与数据信号的输入/输出端口区域(如下图红色区域);

这几个端口诊断出辐射偏高,而端口的连接线材直接延伸到屏蔽箱体之外,完全暴露在空间, 形成天线效应。

由此,我们就诊断出杂讯的源头与传输路径,下一步就是确定改善方案了。

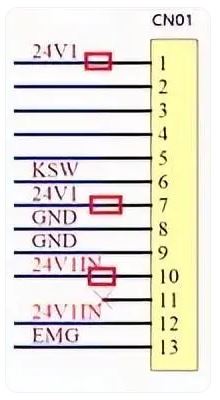

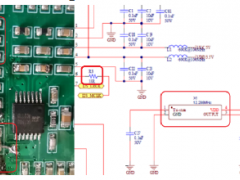

对策 1: 对主板 24V/3.3V,等电源输出端口(如下图端口位置)进行 L/C 滤波处理,对板上数据控制端口增加电容滤波,(根据数据频率点,选择器件规格,L 选择贴片FERRITE BEAD300 欧姆, C 选择贴片300pf/50V 左右。

在增加 FERRITE BEAD 同时增加电容下地滤波。

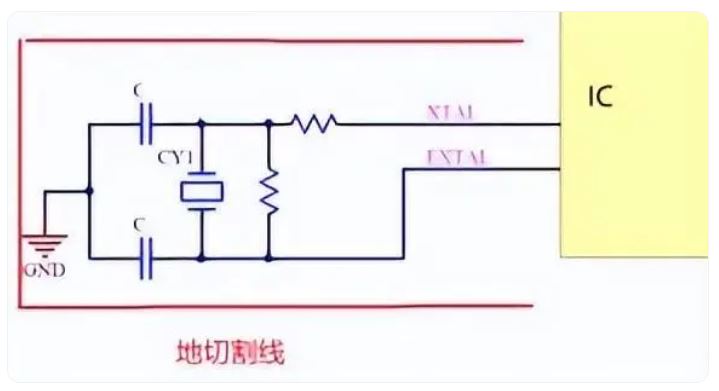

对策 2:对晶振时钟信号地进行切割,让晶振地在最短路径回到,IC 地,尽量保证不串扰到其它区域。

2 . 优化各类线材。

机器内部和外部的连接线材种类繁多,有些接地不良,有些屏蔽不到位,有些走线,方式错误, 等等问题导致相互干扰。

经分析做以下几方面的改善:

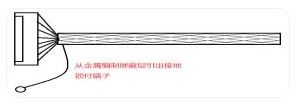

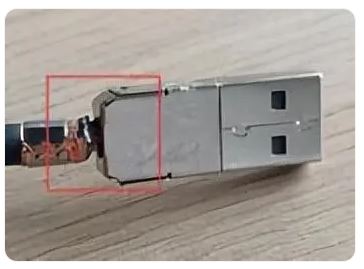

对策1:增加屏蔽线的接地锁付端子,让屏蔽层与数据地就近连接,形成最短回流路径。

对策2 :改善线材端子的接地方式。

线材屏蔽层与端子之间, 由之前的端点连接改为 360金属环焊连接,可以最大 程度防止 clock 信号或 D+/D-差分共模杂讯发散。

对策3:优化线材长度与走线方式。

所有线材减短到最合理的需求长度,线材越长,增加耦合干扰的机会越大。

合理布局走线方式,所有走线避开干扰源周边,电源走线和信号走线分开固定。

苏公网安备32050802011615号

苏公网安备32050802011615号