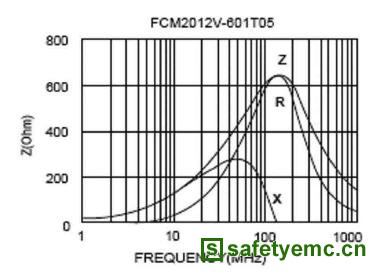

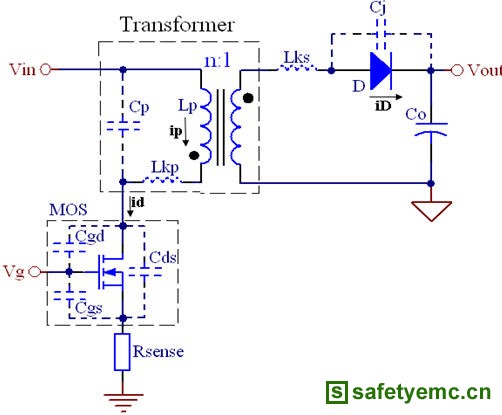

应该非常小心地选择被动器件,以助于优化设计。比如,要想使电源噪声最小化,去耦电容非常必要。这些电容能有效减少环路面积,将辐射发射降到最低。当选取电容时,必须牢记期望的频率范围,这有助于确定合适的电容尺寸。为确定有用的频率范围,要用到两个公式:fPOLE=1/(2π√ LC),fZERO=1/(2πRC)。这里,L代表内部电感,R代表电容的并联电阻。假如电容C=0.01μF,L=1μH,R=1012Ω,利用以上等式,得到电容的频率范围为1.6×10-6 Hz(fPOLE)到1.6MHz(fZERO)。频率高于1.6 MHz,电容就会变成感性。

选择去耦电容时还必须考虑的一个重要因素是IC的瞬态电流,以及需要限制的最大电源电压。比如,如果在10 ns的时间内需要100mA的瞬态电流,并且电源电压的瞬态值必须限制为最大100mV,则电容的容值可确定为:C=I×dt/dV。在这里,电容的最小值为0.01μF。由于陶瓷电容具有较小寄生电感,所以在电源去耦中推荐使用陶瓷电容。电感同样会产生干扰。电感分为空芯和磁芯两种。空芯电感的磁通更大,因而将产生更大干扰。另一方面,磁芯电感中磁通线由于常常被包含在核芯中,因此它们的磁通减少。

电阻有几个重要的参数和规格。除了价格和公差,对给定的设计来说,额定功率对决定最适合的电阻非常关键。电阻的额定功率电阻能承受的不会导致电阻损坏的最高电压。这个电压通过√PR计算,其中P是额定功率,R是电阻值。查看设计中不同电阻的功率衰减曲线是个很好的做法。

选择运算放大器

假如设计中需要精密放大器,而源阻抗又相对较低,则宜选择电压噪声低、相对频率的共模抑制比(CMRR)高、相对频率的电源抑制比(PSRR)高、动态范围宽以及相位裕度高的放大器。作为一个性能指数,运算放大器的电压噪声应该低于10n√Hz。这样,电流噪声则将足够小。

此外,在同一个封装中并联两个或者两个以上放大器可以进一步降低电压噪声,但这样会增加输入电流噪声。例如,AD8512在1kHz时的电压噪声大约是8.5n√Hz。当双列封装的两个运算放大器并联后,输出噪声降低√2倍,总噪声大约等于6 n √Hz。然而,如果源阻抗很高,则电流噪声就要引起注意了。在这种情况下,设计工程师应该将正输入接地并将负输入连接到输出,以对没有用到的双列封装或者四方封装运算放大器进行终端匹配。

牢记的关键点

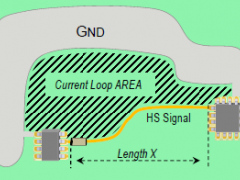

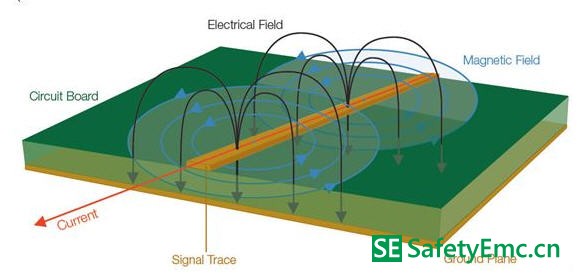

如果可能,尽量使用多层电路板。它们能有效减少环路面积,限制电磁场。另外,去耦电容应靠近电源,电路板上的所有走线应尽可能短。一根长电线会成为传播电磁场的天线。

在测量的时候,卷起探针的地线,并将之靠近实际探测点,可降低直流误差读数。如果有快速转换的器件,走线不能并行,这可避免为辐射创造更大的环路面积。

苏公网安备32050802011615号

苏公网安备32050802011615号