1.1.2 发射工作原理

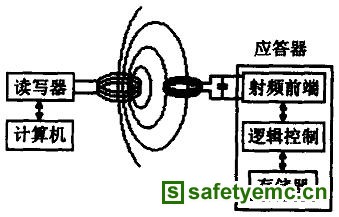

数字基带信号从TX DATA引入TRF6900片内,经过直接数字频率合成器(DDS)调制到中频,再通过锁相环(PLL)倍频到射频,最后通过功率放大器放大信号后,由PA OUT导出射频信号,再通过天线发射出去。

1.1.3 串行控制接口工作原理

串行控制接口包括CLOCK,DATA,STOBE三部分,控制着TRF6900内部所有的寄存器,包括DDS参数设定寄存器和其他的控制寄存器。在CLOCK的每一个上升沿,DATA管脚的逻辑值送入24 b的移位寄存器,当STOBE电平被抬高时,设定的参数被送入选定的锁存器。TRF6900有四个可编程的24 b控制字(A,B,C,D)。控制字A和B分别控制DDS模式0和模式1状态下输出信号频率。控制字C负责锁相环和DDS模式O的设定。控制字D负责调制和DDS模式1的设定。

1.2数字基带部分

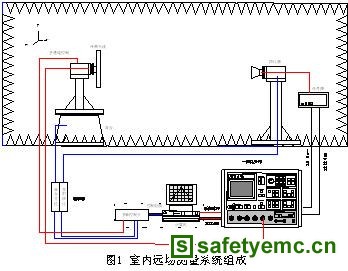

数字基带部分基于微型控制器MSP430F1121。通过它将外部的模拟信号转换为适合TRF6900的数字信号,再配合软件设计可以很方便地进行智能化转换。数字基带部分的硬件电路由RS 232和MSP430F1121组成,如图1所示。

MSP430F112l微型控制器是一款超低功耗、高性能的16位精简指令集MCU,主要由以下部分组成:基础时钟模块,包括1个数控振荡器(DCO)和1个晶体振荡器;看门狗定时器Watchdog Timer,可用作通用定时器;带有3个捕捉/比较寄存器的16位定时器Timer_A;2个具有中断功能的8位并行端口:P1与P2;模拟比较器Comparator A。

2 系统参数计算

2.1 鉴相器的参考频率

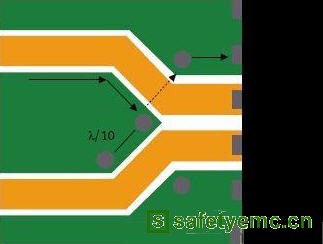

鉴相器是PPL构成锁相环中的单元模块之一,其输入的参考频率是由DDS的输出信号决定的。基于DSS技术的频率合成器能很好地满足各项指标性能,同时也使设计变得简单。鉴相器输出频率的分辨率为:

式中:fpd是鉴相器的最小输入频率,也是DDS时钟频率fref的2°,即最低有效位的权值。TRF6900 DDS累加器有24位,fpd乘以预标值N(可选择256或者512),由它可得出最小频率的步进值为:

累加器的输入是24位的用户串行数据(控制字),时钟基准信号作为累加器的工作时钟信号,两者决定频率的分辨率;输出是一串抽样斜坡数字脉冲,空号频率等于时钟频率。经过D/A转换后得到模拟域的正弦信号fo_DSS,它代表基准相位,即作为鉴相器的基准输入信号。DDS的最终性能主要取决于D/A转换过程中的量化误差以及滤波特性。

苏公网安备32050802011615号

苏公网安备32050802011615号