基于网络的寄生提取是随着版图出现后在整个设计过程中最重要的一个环节。RF设计对于寄生效应非常的敏感。由于设计工程师能够掌握任何区域、走线或模块的相关寄生信息,因此管理不同层次的寄生参数的信息就变得更为重要。不敏感的走线只需要RC参数,而敏感走线则需要RLC参数。带有螺旋电感的走线可以以RLC和电感参数的形式提取出来,甚至可对最敏感的走线添加衬底效应。同时,这些走线可以与无源器件的器件模型混合匹配。

当顶层版图实现后,噪声分析(特别是衬底噪声分析)可以保证有噪电路(如数字逻辑和PLL)不会影响到高度敏感的RF电路。设计工程师可以对此进行检查,如果关注的电路区域被影响到,设计工程师可以修改版图规划或在有噪电路周围增加保护带。然而,想在晶体管级对整个电路进行仿真或包含所有的寄生信息往往是不现实的。一种解决方法是提取行为模型,但这会忽略不同模块间连线的寄生效应,因此必须支持层次化的提取能力和设计模块间连线的寄生参数提取。

7. 校准HDL模型

在模块开发完成后,可以根据关键的电路性能参数对最初的行为模型进行反标注,这样可实现更为精确的HDL级仿真。虽然并不适用于所有效应,但是这种方法能够以更少的运行时间成本获得更为精确的性能信息,并能加速验证,减少全晶体管级验证的工作量。

用混合级仿真对模块进行验证有三个步骤。首先,在对模块功能进行验证时,要在系统级仿真中包含一个理想化的模块模型;然后,用这个模块的网表替换理想化模型来验证模块的功能。这样就能检测出模块缺陷给系统性能带来的影响。

最后,用一个提取模型代替模块的网表。通过对网表和提取模型的仿真结果进行比较分析,可以对提取模型的功能性和精确度进行验证。在以后对其他模块进行混合级仿真时使用经过验证的提取模型而不是理想模型能有效提高其有效性。

如果操作合理,自下而上的验证方式能够对大型系统实现更为详细的验证。由于去掉了物理实现的细节而仅保留行为细节,行为仿真的执行速度非常快。随着模块逐渐成熟,由自下而上验证过程生成的行为模型越来越有用,并可用于第三方IP验证和复用。

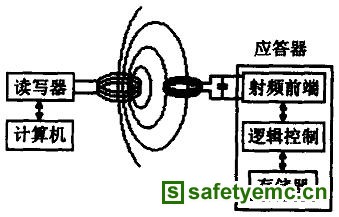

对于包括射频前端的无线系统来说,自下而上的验证过程是验证大型系统性能的必然方法。如前所述,晶体管级的RF系统验证需要将调制信号运行数千个周期,这往往是不现实的。用先进的包络分析技术替代传统的瞬态仿真只能将仿真速度提高10~20倍。即使将传统的通带模型用于自下而上的提取技术,由于RF载频仍然存在,也无法将仿真速度提高到令人满意的程度。只有将自下而上的模型提取技术和复杂的基带或低通等效模型结合起来,载波信号才会被有效抑止,其仿真时间才足以实现全芯片级的误包率分析。

为所有模块都生成行为模型是一件耗时费力的工作,而且只有极少的设计工程师具有这种专业技术。而自动化的工具和方法学能够根据特定应用和技术需要,借助经过验证的精度和开放API来修改现有模板生成详细的行为模型。

苏公网安备32050802011615号

苏公网安备32050802011615号