1. 电源隔离及电压转换

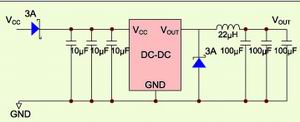

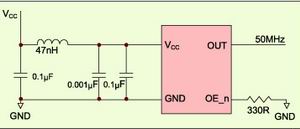

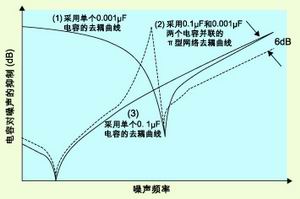

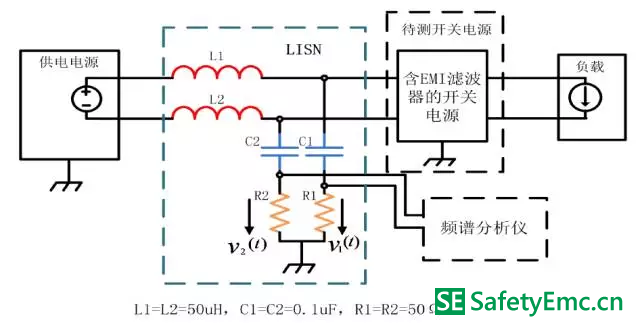

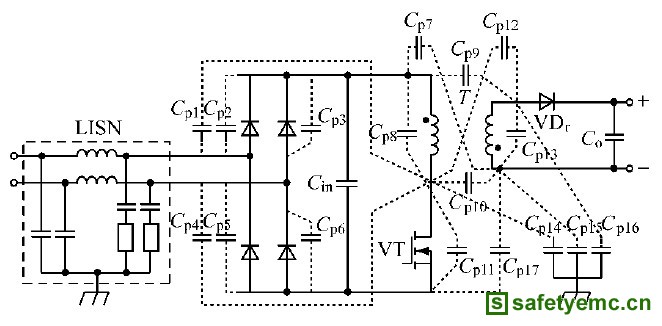

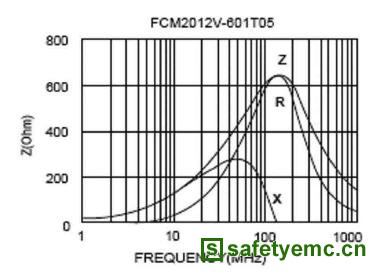

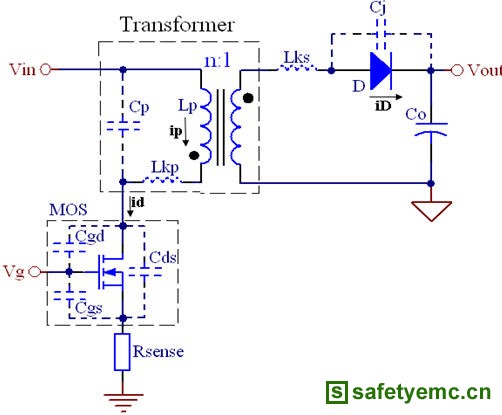

外部直流供电电源采用线性电源供电,纹波较小,但直流噪声仍然可达到50mV,通过DC- DC模块进行能量转换后,噪声可降低到25mV以下,由于DC-DC对高频进行了很好的抑制,因此,电源部分带来的噪声不会串到高频系统中。在DC-DC模块输入端加整流和电容滤波处理,是在DC-DC模块之前对噪声的抑制。DC-DC输出端加稳压处理是为了保证对供电器件的保护,同时加电容对输出的低频部分进一步做滤波处理。在控制系统中,可编程逻辑器件的供电并不是单电压的,还需要DC-DC输出的5V直流通过LDO进行变压,LDO对DC-DC输出的电压中的噪声部分还可进一步抑制,尤其是对高频部分,通过2个LDO,将5V直流电压变到3.3V和1.5V两组输出到可编程器件。DC-DC去耦处理如图2。

2. 接地部分设计

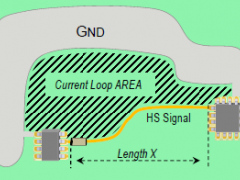

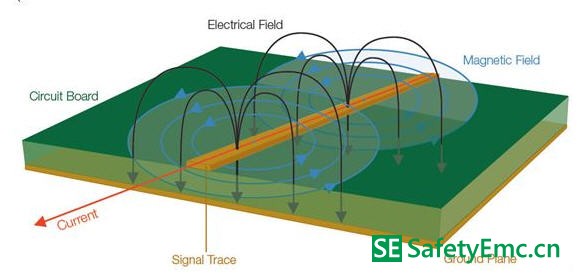

此控制系统采用四层PCB设计,具有完整的地平面,可以对信号提供低阻抗返回路径,因此可以降低信号对外界造成的辐射。对于接地部分,有单点接地和多点接地两种设计。对于1MHz以下的部分采用单点接地,这时分布阻抗的影响较小。对于1MHz或更高频率的电路部分,返回路径的电感会对电路产生作用,产生压降或射频电流,因此高于1MHz的电路部分采用多点接地。多点接地可以减少噪声产生电路与参考面间的电感。

时钟信号线最大走线长度计算

采用有源时钟主要是为可编程逻辑器件提供参考信号,时钟的精度可以直接决定控制电路的性能。本设计中时钟的精度采用30ppm,通过可编程逻辑器件内的锁相环电路,实现对参考时钟的同步。有源时钟由外部直接供电(3.3V),即可输出时钟信号,时钟输出信号升降沿基本为4~6ns,在设计时,时钟信号线的走线长度不应超过电长走线,超过此长度的线叫电气长线,就会产生传输线效应。采用基本公式计算时钟信号单程最长走线的公式为:

L=(tr/2)*VP

VP=

L:在微带线(micro strip line)中电气长线长度;

tr:信号上升沿时间,取4ns;

VP:信号在微带线中传输的速度;

C:光速

ε:元件层与地平面的相对介电常数,通常取4.5。

按上述公式计算的时钟信号在微带线中传输的速度为1.414*108m/s,因此,始终信号线最大走线长度28.3cm。

苏公网安备32050802011615号

苏公网安备32050802011615号