电路的逻辑部分设计

逻辑部分主要包括逻辑输入、逻辑输出、数据缓冲和终端匹配4个部分,逻辑的产生靠可编程逻辑器件来完成,由于产生的是低压逻辑信号,因此需要高速CMOS器件进行缓冲,来驱动控制设备。

1.逻辑输入

对于低电压可编程逻辑器件来说,如果输入信号电平偏高,通常在信号输入端串接一限流电阻,阻值根据具体器件和电压差而定,对于此设计电路来说,输入信号为标准TTL信号,而可编程逻辑器件输入电平最大为3.3V兼容,因此在输入信号与可编程器件之间串接一个100欧姆电阻进行限流,以保证可编程器件的使用安全。

2.逻辑输出

为了保证输出的同步性,在可编程逻辑器件内部,对输出信号做了锁存。同时,可编程逻辑器件内部的布线也是很复杂的,通常器件厂家总是公布对逻辑布线进行了很大的升级、改进,但仍然有很大的提升空间,因此,通过人为的逻辑控制以及内部的布局控制,对于改善信号输出性能会带来一定的改善。这就好比很多PCB厂商,虽然软件本身的自动布线功能一再改善,但多数情况下还是达不到完全理想的性能,还需手工修改进行补偿。

3.数据缓冲

可编程逻辑器件只是实现了逻辑关系的产生,但输出的数据驱动能力和传输距离都受到了很大的限制,因此还需要加数据缓冲来对控制设备的驱动。设计中采用高速CMOS器件进行数据缓冲,具有高扇出电流、高速、功耗低等特点,但此控制电路控制信号传输距离为30米,以此需要将TTL转为差分控制,接收端在将差分信号转为TTL信号,即可实现高速远距离的控制。

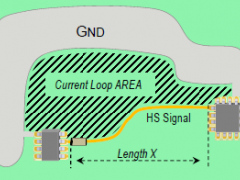

4.终端匹配

对于差分传输,1M频率的信号通常可传输90米作用,但为了保证信号的完整性,通常在差分接收端加120欧姆平衡电阻,同时在信号线上串接一匹配电阻。本设计根据实际需要选用51欧姆匹配电阻,不同的情况需要做调整。

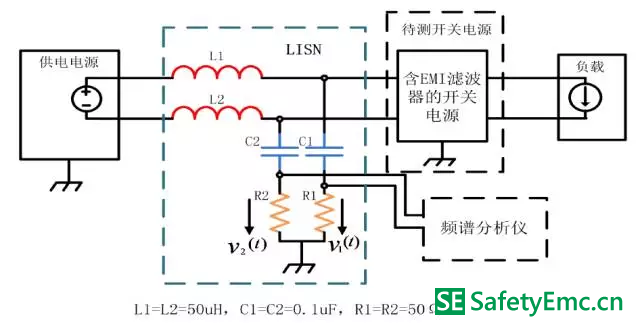

电路的接口部分设计

电路的接口部分采用DB型插头进行差分信号的传输,差分信号在传输时不容易辐射干扰,但由于阻抗不匹配造成的干扰还是可能产生误码的。插头采用弯针焊接到PCB上,弯针和焊接孔将会产生一定的电感,造成传输路径的不匹配,由于阻抗不匹配造成信号在接插件处反射,对后面一级控制系统产生EMI。将接插头的外壳接到数字地,在接到系统地的低阻抗回路就会对接插头处的反射噪声信号提供一个低阻抗回路,从而减小对下一级电路的影响。当然,主要的消除措施是在接收端加终端匹配。

苏公网安备32050802011615号

苏公网安备32050802011615号